# **M**•CORE

Reference Manual with M210/M210S Specifications

HCMOS Microcontroller Unit

# M•CORE with M210/M210S Specifications

**Reference Manual**

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and (A) are registered trademarks of Motorola, Inc. DigitalDNA, M•CORE, and OnCE are a trademarks of Motorola, Inc.

© Motorola, Inc., 2001

Reference Manual

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.motorola.com/semiconductors/

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

| Date            | Revision<br>Level | Description                                             | Page<br>Number(s) |

|-----------------|-------------------|---------------------------------------------------------|-------------------|

| September, 2001 | 1.0               | Complete reformat adding M210/M210S core specifications | Throughout        |

#### **Revision History**

**Reference Manual**

# **List of Sections**

| Section 1. Overview                                                |

|--------------------------------------------------------------------|

| Section 2. Registers                                               |

| Section 3. Instructions                                            |

| Section 4. Exception Processing                                    |

| Section 5. Core Interface                                          |

| Section 6. Interface Operation                                     |

| Section 7. Hardware Accelerator Interface (HAI)219                 |

| Section 8. JTAG Test Access Port and OnCE247                       |

| Appendix A. Nomenclature                                           |

| Appendix B. M210 and M210S Core Instruction<br>Pipeline and Timing |

| Appendix C. M210/M210S Core Interface                              |

| Appendix D. M210/M210S Interface Operation329                      |

| Index                                                              |

M•CORE with M210/M210S Specifications - Rev. 1.0

6

# **Table of Contents**

## Section 1. Overview

| 1.1 | Contents                        |

|-----|---------------------------------|

| 1.2 | Introduction                    |

| 1.3 | Features                        |

| 1.4 | Microarchitecture Summary       |

| 1.5 | Programming Model               |

| 1.6 | Data Format Summary             |

| 1.7 | Operand Addressing Capabilities |

| 1.8 | Instruction Set Overview        |

#### Section 2. Registers

| 2.1     | Contents                                          |

|---------|---------------------------------------------------|

| 2.2     | Introduction                                      |

| 2.3     | User Programming Model40                          |

| 2.3.1   | General-Purpose Registers                         |

| 2.3.2   | Program Counter                                   |

| 2.3.3   | Condition Code/Carry Bit41                        |

| 2.4     | Supervisor Programming Model                      |

| 2.4.1   | Alternate Register File43                         |

| 2.4.2   | Processor Status Register                         |

| 2.4.2.  | 1 Updates to the PSR                              |

| 2.4.2.2 | 2 Exception Recognition and Processing Updates 48 |

| 2.4.2.  | 3 RTE and RFI Instruction Updates                 |

| 2.4.2.4 | 4 MTCR Instruction Updates                        |

| 2.4.3   | Vector Base Register                              |

M•CORE with M210/M210S Specifications - Rev. 1.0

**Reference Manual**

| 2.4.4 | Supervisor Storage Registers |

|-------|------------------------------|

| 2.4.5 | Exception Shadow Registers   |

| 2.4.6 | Global Control Register      |

| 2.4.7 | Global Status Register       |

## **Section 3. Instructions**

| 3.1    | Contents                                          | 53 |

|--------|---------------------------------------------------|----|

| 3.2    |                                                   | 54 |

| 3.3    | Instruction Types and Addressing Modes            | 54 |

| 3.3.1  | Register-to-Register Instructions                 | 54 |

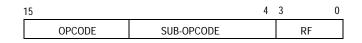

| 3.3.1. | .1 Monadic Register Addressing Mode               | 55 |

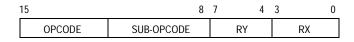

| 3.3.1. | .2 Dyadic Register Addressing Mode                | 56 |

| 3.3.1. | .3 Register with 5-Bit Immediate Mode             | 57 |

| 3.3.1. | .4 Register with 5-Bit Offset Immediate Mode      | 58 |

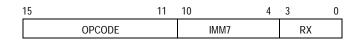

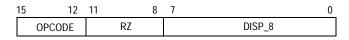

| 3.3.1. | .5 Register with 7-Bit Immediate Mode             | 58 |

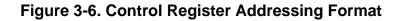

| 3.3.1. | .6 Control Register Addressing Mode               | 59 |

| 3.3.2  | Data Memory Access Instructions                   | 59 |

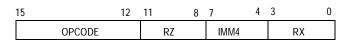

| 3.3.2. | .1 Scaled 4-Bit Immediate Addressing Mode         | 59 |

| 3.3.2. | .2 Load/Store Register Quadrant Mode              | 59 |

| 3.3.2. | .3 Load/Store Multiple Register Mode              | 60 |

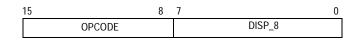

| 3.3.2. | .4 Load Relative Word Mode                        | 60 |

| 3.3.3  | Flow Control Instructions                         | 61 |

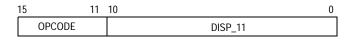

| 3.3.3. | .1 Scaled 11-Bit Displacement Mode                | 61 |

| 3.3.3. | 5 5                                               |    |

| 3.3.3. | .3 Indirect Mode                                  | 61 |

| 3.3.3. | .4 Register with 4-Bit Negative Displacement Mode | 62 |

| 3.4    | Opcode Map                                        | 63 |

| 3.5    | Instruction Set.                                  | 67 |

## **Section 4. Exception Processing**

| 4.1 | Contents                      | 163 |

|-----|-------------------------------|-----|

| 4.2 | Introduction                  | 164 |

| 4.3 | Exception Processing Overview | 164 |

| Reference | Manual |

|-----------|--------|

|-----------|--------|

| 4.4 Stages of Exception P    | rocessing165                          |

|------------------------------|---------------------------------------|

| 4.5 Exception Vectors        |                                       |

| 4.6 Exception Types          |                                       |

| 4.6.1 Reset Exception (Ve    | ector Offset 0x0)169                  |

| 4.6.2 Misaligned Access      | Exception (Vector Offset 0x4)169      |

| 4.6.3 Access Error Excep     | tion (Vector Offset 0x8)170           |

| 4.6.4 Divide-by-Zero Exce    | eption (Vector Offset 0x0C)170        |

| 4.6.5 Illegal Instruction Ex | cception (Vector Offset 0x10)170      |

| 4.6.6 Privilege Violation E  | Exception (Vector Offset 0x14)171     |

| 4.6.7 Trace Exception (Ve    | ector Offset 0x18)171                 |

| 4.6.8 Breakpoint Exception   | on (Vector Offset 0x1C)173            |

| 4.6.9 Unrecoverable Erro     | r Exception (Vector Offset 0x20)173   |

| 4.6.10 Soft Reset Exception  | n (Vector Offset 0x24)173             |

| 4.6.11 Interrupt Exceptions  | s                                     |

| 4.6.11.1 Normal Interrupt    | (INT)                                 |

| 4.6.11.2 Fast Interrupt (FI  | NT)                                   |

| 4.6.12 Hardware Accelerat    | cor Exception (Vector Offset 0x30)176 |

| 4.6.13 Instruction Trap Exc  | ception (Vector Offset 0x40-0x5C)176  |

| 4.7 Exception Priorities     |                                       |

| 4.8 Returning from Except    | ion Handlers178                       |

## Section 5. Core Interface

| Contents                    |

|-----------------------------|

| Introduction                |

| Signal Descriptions         |

| Address Bus (ADDR[31:0])185 |

| Data Bus (DATA[31:0])       |

| Transfer Request (TREQ)185  |

| Transfer Busy (TBUSY)185    |

| Transfer Abort (ABORT)185   |

| Transfer Attribute Signals  |

| Transfer Code (TC[2:0])     |

| Read/Write (R/W)186         |

|                             |

| 5.4.3       Transfer Size (TSIZ[1:0])                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.5Transfer Control Signals1875.5.1Transfer Acknowledge (TA)1875.5.2Transfer Error Acknowledge (TEA)1885.5.3Breakpoint Request (BRKRQ)188                                                                              |

| 5.6Memory Management Control Signals1885.6.1Translate Control (TE)1885.6.2Soft Reset (SRST)188                                                                                                                         |

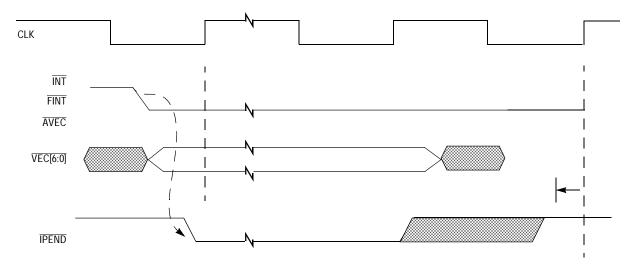

| 5.7Interrupt Control Signals.1895.7.1Normal Interrupt Request (INT)1895.7.2Fast Interrupt Request (FINT)1895.7.3Interrupt Pending Status (IPEND)1895.7.4Interrupt Vector Number (VEC[6:0])1895.7.5Autovector (AVEC)190 |

| 5.8 Power Management Control Signals                                                                                                                                                                                   |

| 5.9         Status and Clock Signals         191           5.9.1         Processor Status (PSTAT[3:0])         191           5.9.2         M•CORE Processor Clock (CLK)         192                                    |

| 5.10 Global Status and Control Interface                                                                                                                                                                               |

| 5.11 Hardware Accelerator Interface                                                                                                                                                                                    |

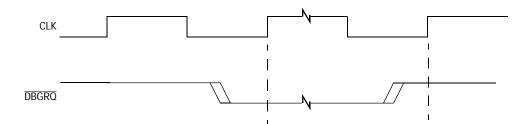

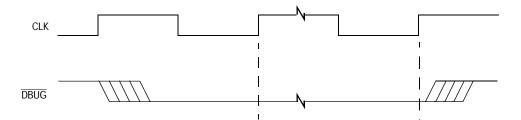

| 5.12Debug/Emulation Support Signals1935.12.1Debug Request (DBGRQ)1935.12.2Debug Acknowledge (DBUG)193                                                                                                                  |

| 5.13 Test Signals                                                                                                                                                                                                      |

| 5.14 Power Supply Connections                                                                                                                                                                                          |

| 5.15 Signal Summary                                                                                                                                                                                                    |

## Section 6. Interface Operation

| 6.1                                              | Contents                                                                                                                                                                                                                                           |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2                                              | Introduction                                                                                                                                                                                                                                       |

| 6.3                                              | Bus Characteristics                                                                                                                                                                                                                                |

| 6.4                                              | Data Transfer Mechanism                                                                                                                                                                                                                            |

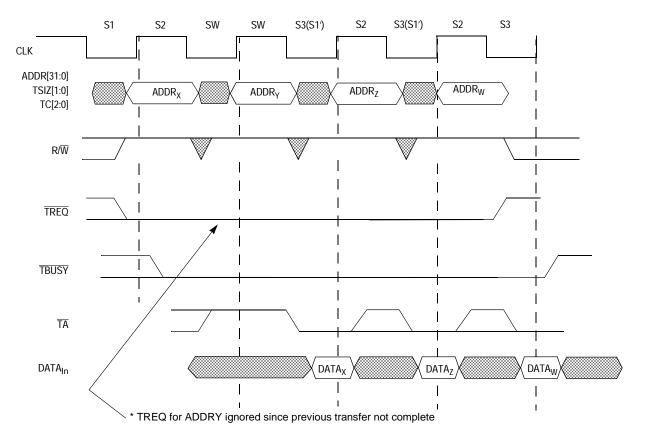

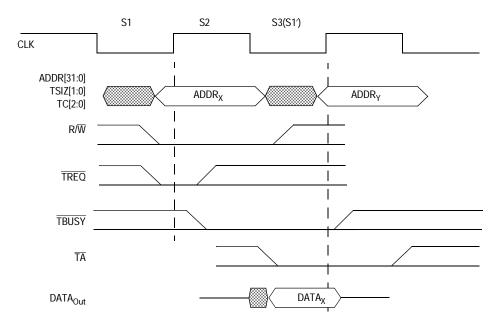

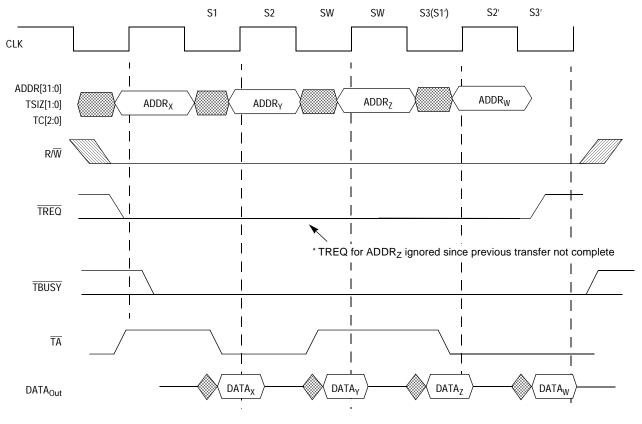

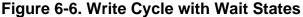

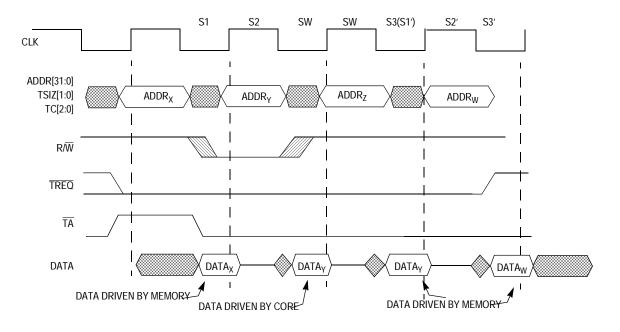

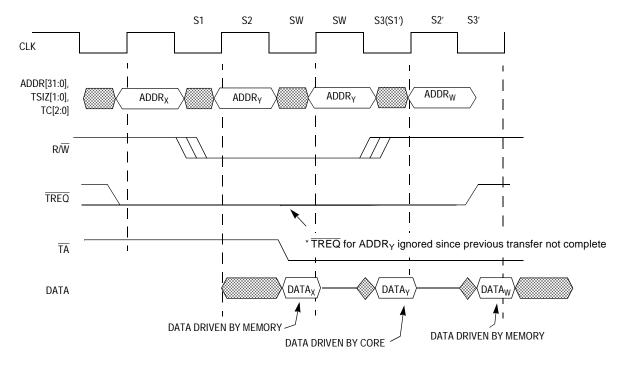

| 6.5<br>6.5.1<br>6.5.2<br>6.5.3<br>6.5.4<br>6.5.5 | Processor Instruction/Data Transfers199Instruction and Data Read Transfer Cycles200Read Transfer Cycles with Wait State(s)202Write Transfer Cycles202Write Transfer Cycles with Wait State(s)205Data Bus Hand-Off Between Read and Write Cycles206 |

| 6.6<br>6.6.1<br>6.6.2                            | Exception Bus Control Cycles                                                                                                                                                                                                                       |

| 6.7                                              | ABORT Signal Operation                                                                                                                                                                                                                             |

| 6.8                                              | D2A Signal Operation                                                                                                                                                                                                                               |

| 6.9<br>6.9.1<br>6.9.2                            | Reset Operation.211Hard Reset (Power-On Reset).211Soft Reset211                                                                                                                                                                                    |

| 6.10                                             | Memory Management Interface Operation                                                                                                                                                                                                              |

| 6.11                                             | Interrupt Interface Operation                                                                                                                                                                                                                      |

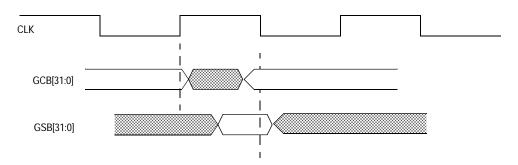

| 6.12                                             | Global Status and Control Interface Operation214                                                                                                                                                                                                   |

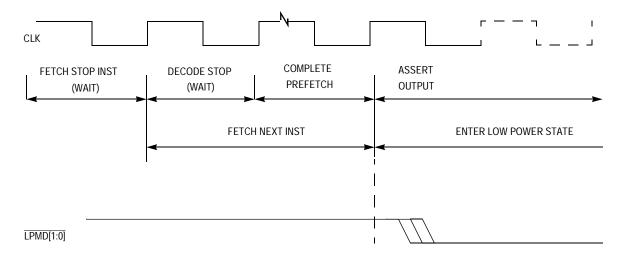

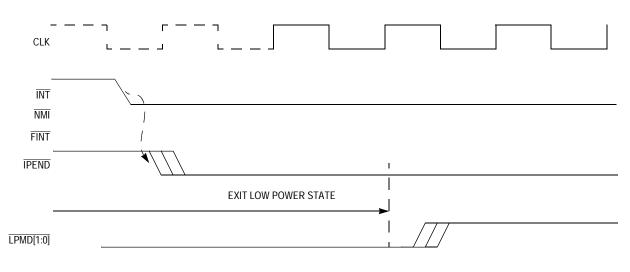

| 6.13                                             | Power Management Interface Operation                                                                                                                                                                                                               |

| 6.14                                             | Emulation/Debug Interface Operation                                                                                                                                                                                                                |

| ţ                                                | Section 7. Hardware Accelerator Interface (HAI)                                                                                                                                                                                                    |

| 7.1                                              | Contents                                                                                                                                                                                                                                           |

|                                                         | Register Snooping Mechanism                                                                                                       | 21                                           |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

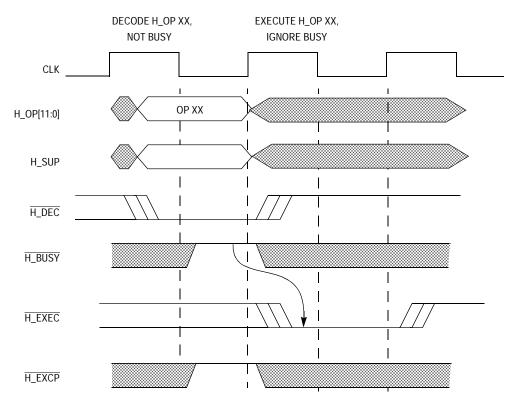

| 7.5<br>7.5.1<br>7.5.2                                   | Instruction Transfer Mechanism       22         Control Handshake       22         Driving the H_BUSY and H_EXCP Signals       22 | 22                                           |

| 7.6<br>7.6.1<br>7.6.2<br>7.6.2                          | —                                                                                                                                 | 30<br>33<br>33                               |

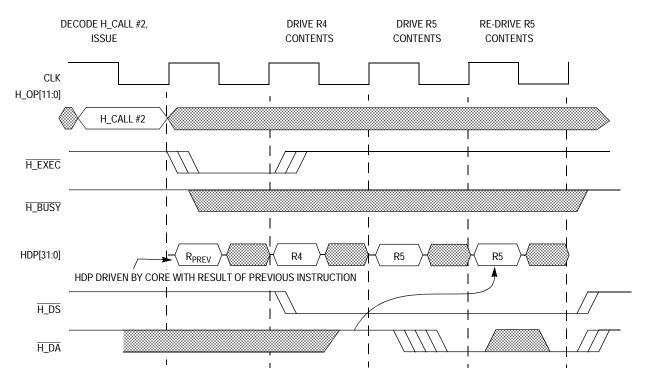

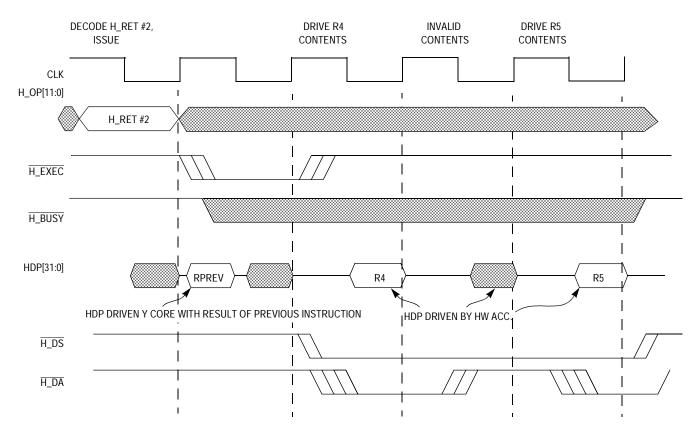

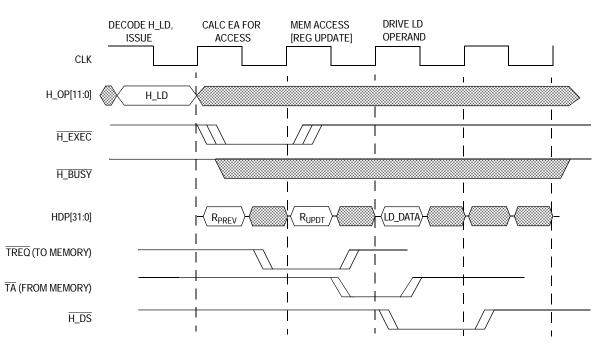

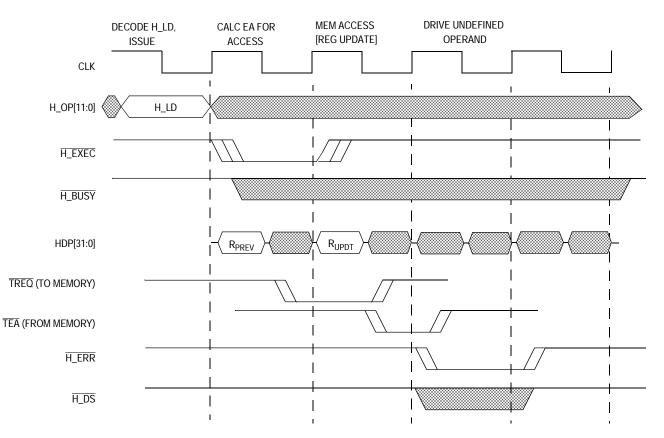

| 7.7<br>7.7.1<br>7.7.2<br>7.7.3<br>7.7.4<br>7.7.5        | Instruction Primitives.23H_CALL Primitive23H_RET Primitive23H_LD Primitive23H_ST Primitive24H_EXEC Primitive24                    | 38<br>39<br>39<br>40<br>41                   |

| 7.8                                                     | Instruction Primitive Glossary                                                                                                    | 41                                           |

|                                                         | Section 8 JTAG Test Access Port and OnCE                                                                                          |                                              |

| 8.1                                                     | Section 8. JTAG Test Access Port and OnCE Contents                                                                                | 47                                           |

| 8.1<br>8.2                                              |                                                                                                                                   |                                              |

| -                                                       | Contents                                                                                                                          | 49<br>51<br>52<br>52<br>52<br>52<br>52       |

| 8.2<br>8.3<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4<br>8.3.5 | Contents                                                                                                                          | 49<br>51<br>52<br>52<br>52<br>52<br>52<br>52 |

**Reference Manual**

| 8.5.5 HIGHZ Instruction                        |

|------------------------------------------------|

| 8.5.6 CLAMP Instruction                        |

| 8.5.7 BYPASS Instruction                       |

| 8.6 IDCODE Register                            |

| 8.7 Bypass Register                            |

| 8.8 Boundary SCAN Register                     |

| 8.9 Restrictions                               |

| 8.10 Non-Scan Chain Operation                  |

| 8.11 Boundary Scan                             |

| 8.12 Low-Level TAP (OnCE) Module               |

| 8.13 Signal Descriptions                       |

| 8.13.1 Debug Serial Input (TDI)                |

| 8.13.2 Debug Serial Clock (TCLK)               |

| 8.13.3 Debug Serial Output (TDO)               |

| 8.13.4 Debug Mode Select (TMS)270              |

| 8.13.5 Test Reset (TRST)                       |

| 8.13.6 Debug Event (DE)                        |

| 8.14 Functional Description                    |

| 8.14.1 Operation                               |

| 8.14.2 OnCE Controller and Serial Interface    |

| 8.14.3 OnCE Interface Signals                  |

| 8.14.3.1 Internal Debug Request Input (IDR)273 |

| 8.14.3.2 CPU Debug Request (DBGRQ)             |

| 8.14.3.3 CPU Debug Acknowledge (DBGACK)274     |

| 8.14.3.4 CPU Breakpoint Request (BRKRQ)274     |

| 8.14.3.5 CPU Address, Attributes (ADDR, ATTR)  |

| 8.14.3.6 CPU Status (PSTAT)                    |

| 8.14.3.7 OnCE Debug Output (DEBUG)             |

| 8.14.4 OnCE Controller Registers               |

| 8.14.4.1 OnCE Command Register                 |

| 8.14.4.2 OnCE Control Register                 |

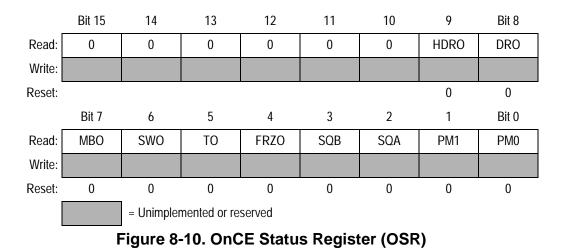

| 8.14.4.3 OnCE Status Register                  |

| 8.14.5 OnCE Decoder (ODEC)                     |

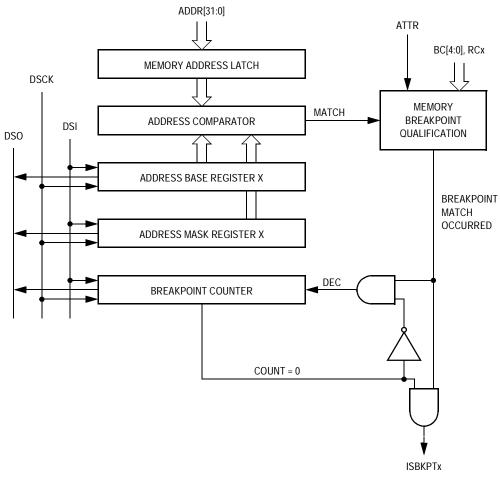

| 8.14.6 Memory Breakpoint Logic                              |

|-------------------------------------------------------------|

| 8.14.6.1 Memory Address Latch (MAL)                         |

| 8.14.6.2 Breakpoint Address Base Registers                  |

| 8.14.7 Breakpoint Address Mask Registers                    |

| 8.14.7.1 Breakpoint Address Comparators                     |

| 8.14.7.2 Memory Breakpoint Counters                         |

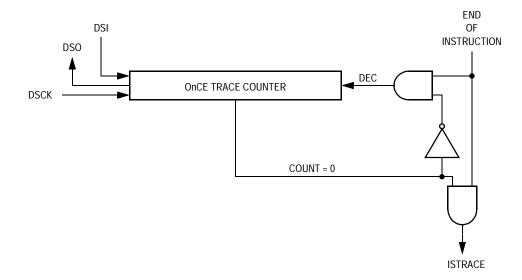

| 8.14.8 OnCE Trace Logic                                     |

| 8.14.8.1 OnCE Trace Counter                                 |

| 8.14.8.2 Trace Operation                                    |

| 8.14.9 Methods of Entering Debug Mode                       |

| 8.14.9.1 Debug Request During RESET                         |

| 8.14.9.2 Debug Request During Normal Activity               |

| 8.14.9.3 Debug Request During Stop, Doze,                   |

| or Wait Mode                                                |

| 8.14.9.4 Software Request During Normal Activity            |

| 8.14.10 Enabling OnCE Trace Mode                            |

| 8.14.11 Enabling OnCE Memory Breakpoints                    |

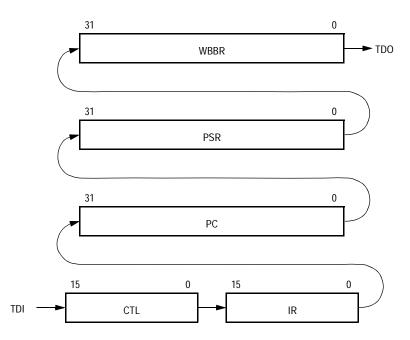

| 8.14.12 Pipeline Information and Write-Back Bus Register290 |

| 8.14.12.1 Program Counter Register                          |

| 8.14.12.2 Instruction Register                              |

| 8.14.12.3 Control State Register                            |

| 8.14.12.4 Writeback Bus Register                            |

| 8.14.12.5 Processor Status Register                         |

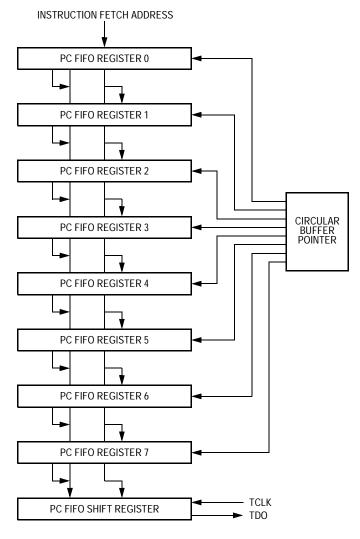

| 8.14.13 Instruction Address FIFO Buffer (PC FIFO)           |

| 8.14.14 Reserved Test Control Registers                     |

| 8.14.15 Serial Protocol                                     |

| 8.14.16 OnCE Commands                                       |

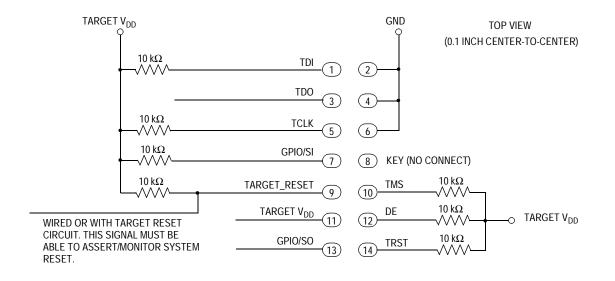

| 8.14.17 Target Site Debug System Requirements               |

| 8.14.18 Interface Connector for JTAG/OnCE Serial Port       |

## Appendix A. Nomenclature

| A.1 | Contents           |

|-----|--------------------|

| A.2 | Introduction       |

| A.3 | References         |

| A.4 | Units and Measures |

| Reference | Manual |

|-----------|--------|

|-----------|--------|

| A.5 | Symbology   | .300 |

|-----|-------------|------|

| A.6 | Terminology | .300 |

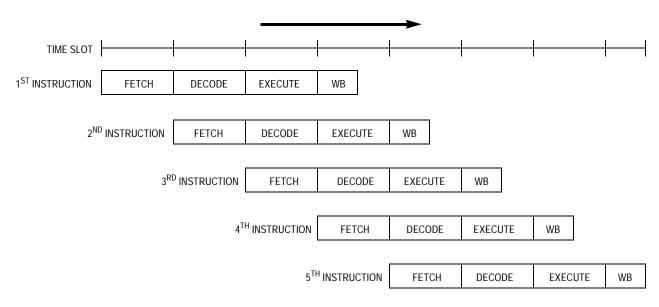

## Appendix B. M210 and M210S Core Instruction Pipeline and Timing

| B.1 | Contents                   |

|-----|----------------------------|

| B.2 | Introduction               |

| B.3 | Instruction Pipeline       |

| B.4 | Instruction Execution Time |

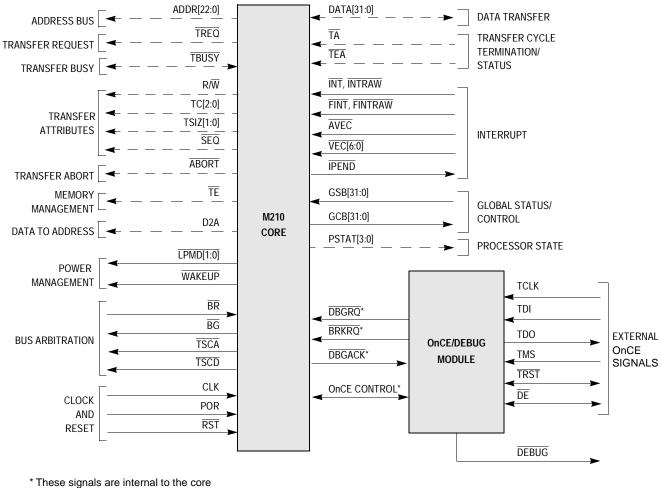

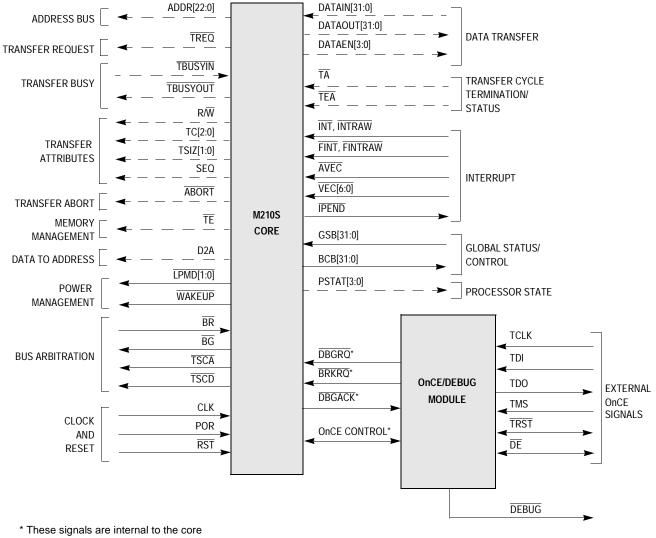

## Appendix C. M210/M210S Core Interface

| C.1    | Contents                                                    |

|--------|-------------------------------------------------------------|

| C.2    | Introduction                                                |

| C.3    | M210 Core Interface Overview                                |

| C.4    | MLB Signal Descriptions                                     |

| C.4.1  | Bus Signals                                                 |

| C.4.1. | 1 Address Bus (ADDR[22:0])                                  |

| C.4.1. | 2 Data Bus (DATA[31:0])                                     |

| C.4.1. | 3 Input Data Bus (DATA <sub>In</sub> [31:0])                |

| C.4.1. | 4 Output Data Bus (DATA <sub>Out</sub> [31:0])              |

| C.4.1. | 5 Data Bus Byte Output Enable (DATA <sub>EN</sub> [3:0])317 |

| C.4.2  | Transfer Control                                            |

| C.4.2. | 1 Transfer Acknowledge (TA)                                 |

| C.4.2. | 2 Transfer Error Acknowledge (TEA)                          |

| C.4.2. |                                                             |

| C.4.2. | 4 Transfer Busy (TBUSY)                                     |

| C.4.2. | 5 Transfer Busy Output (TBUSYOUT)                           |

| C.4.2. | 6 Transfer Busy Input (TBUSYIN)                             |

| C.4.2. | 7 Transfer Abort (ABORT)                                    |

| C.4.3  | Transfer Attribute Signals                                  |

| C.4.3. | 1 Transfer Code (TC[2:0])                                   |

| C.4.3. | 2 Read/Write (R/W)                                          |

|        |                                                             |

| C.4.3.3 | Transfer Size (TSIZ[1:0])                   | 320 |

|---------|---------------------------------------------|-----|

| C.4.3.4 | Sequential Access (SEQ)                     | 320 |

| C.4.4   | Translate Control (TE)                      | 320 |

| C.4.5   | Data to Address Signal (D2A)                | 320 |

| C.4.6   | Processor Status Signals                    | 321 |

| C.4.6.1 | Processor Status (PSTAT[3:0])               | 321 |

|         | Other Processor Signals                     |     |

| C.5.1   | Master Clock (MCLK)                         | 322 |

| C.5.2   | Reset Control Signals.                      |     |

| C.5.2.1 | Master Reset (RST)                          |     |

| C.5.2.2 | Power-On Reset (POR)                        |     |

| C.5.3   | Bus Arbitration Control Signals             |     |

| C.5.3.1 | Bus Request (BR)                            |     |

| C.5.3.2 | Bus Grant (BG)                              |     |

| C.5.3.3 | Three-State Control Address (TSCA)          |     |

| C.5.3.4 | Three-State Control Data (TSCD)             | 323 |

| C.5.4   | Power Management Control Signals            |     |

| C.5.4.1 | Low-Power Mode (LPMD[1:0])                  |     |

| C.5.4.2 | Wakeup (WAKEUP)                             |     |

| C.5.5   | Global Status and Control Interface Signals | 325 |

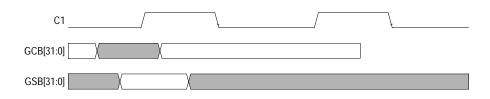

| C.5.5.1 | Global Control (GCB[31:0])                  | 325 |

| C.5.5.2 | Global Status (GSB[31:0])                   | 325 |

| C.5.6   | Interrupt Control Signals                   |     |

| C.5.6.1 | Normal Interrupt Request (INT)              |     |

| C.5.6.2 | Raw Normal Interrupt Request (INTRAW)       |     |

| C.5.6.3 | Fast Interrupt Request (FINT)               |     |

| C.5.6.4 | Raw Fast Interrupt Request (FINTRAW)        |     |

| C.5.6.5 | Interrupt Pending (IPEND)                   |     |

| C.5.6.6 | Interrupt Vector Number (VEC[6:0])          |     |

| C.5.6.7 | Autovector (AVEC)                           |     |

| C.5.7   | Power Supply Connections                    | 327 |

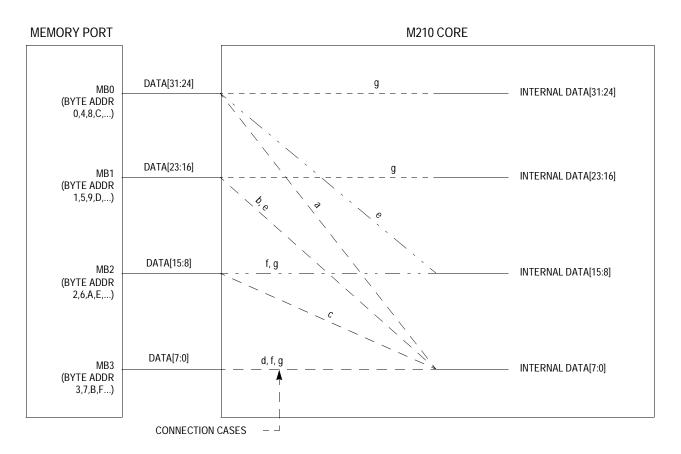

## Appendix D. M210/M210S Interface Operation

| D.1 | Contents            | 329 |

|-----|---------------------|-----|

| D.2 | Introduction        | 330 |

| D.3 | Bus Characteristics | 330 |

**Reference Manual**

| D.4 Data Transfer Mechanism                                                                          |

|------------------------------------------------------------------------------------------------------|

| D.5Processor Instruction/Data Transfers                                                              |

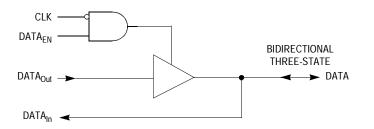

| D.6 Bidirectional Three-State Data Bus                                                               |

| D.7 Bus Exception Control Cycles                                                                     |

| D.8 Bus Errors                                                                                       |

| D.9 Abort SIgnal Operation                                                                           |

| D.10 Data to Address Transfer Operation                                                              |

| D.11 Breakpoint Request Operation                                                                    |

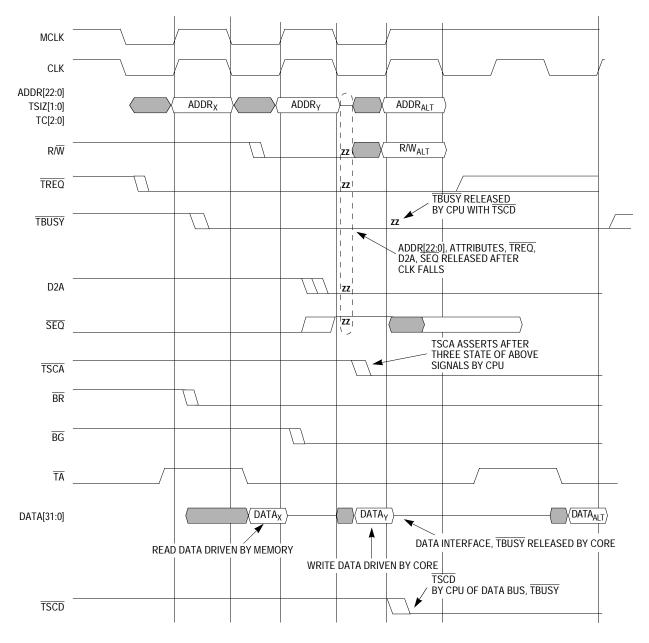

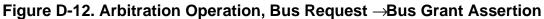

| D.12 Bus Arbitration Operation346D.12.1 Operation Examples348D.12.2 Interaction with Low-Power Modes |

| and Debug Operation                                                                                  |

| D.13       Reset Operation                                                                           |

| D.14 Interrupt Interface Operation                                                                   |

| D.15 Global Status and Control Interface Operation                                                   |

| D.16 Power Management Interface Operation                                                            |

| D.17 Emulation/Debug Interface Operation                                                             |

#### Index

## Reference Manual — M•CORE with M210/M210S Specifications

# **List of Figures**

| Figur | e Title                                            | Page |

|-------|----------------------------------------------------|------|

| 1-1   | Programming Model                                  | 32   |

| 1-2   | Data Organization in Memory                        | 33   |

| 1-3   | Data Organization in Registers                     | 34   |

| 2-1   | User Programming Model                             |      |

| 2-2   | Supervisor Additional Resources                    |      |

| 2-3   | Processor Status Register (PSR)                    |      |

| 2-4   | Vector Base Register (VBR)                         | 50   |

|       |                                                    |      |

| 3-1   | Monadic Format                                     |      |

| 3-2   | Dyadic Format                                      |      |

| 3-3   | Register with 5-Bit Immediate Format               |      |

| 3-4   | Register with 5-Bit Offset Immediate Format        |      |

| 3-5   | Register with 7-Bit Immediate Format               |      |

| 3-6   | Control Register Addressing Format                 |      |

| 3-7   | Scaled 4-Bit Immediate Format                      |      |

| 3-8   | Load/Store Register Quadrant Format                |      |

| 3-9   | Load/Store Multiple Registers Format               |      |

| 3-10  | Load Relative Word Format                          |      |

| 3-11  | Scaled 11-Bit Displacement Format                  |      |

| 3-12  | Register Addressing Format                         |      |

| 3-13  | Indirect Format                                    |      |

| 3-14  | Register with 4-Bit Displacement Addressing Format | 62   |

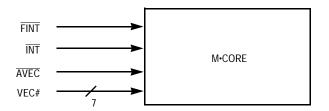

| 4-1   | Interrupt Interface Signals                        | 175  |

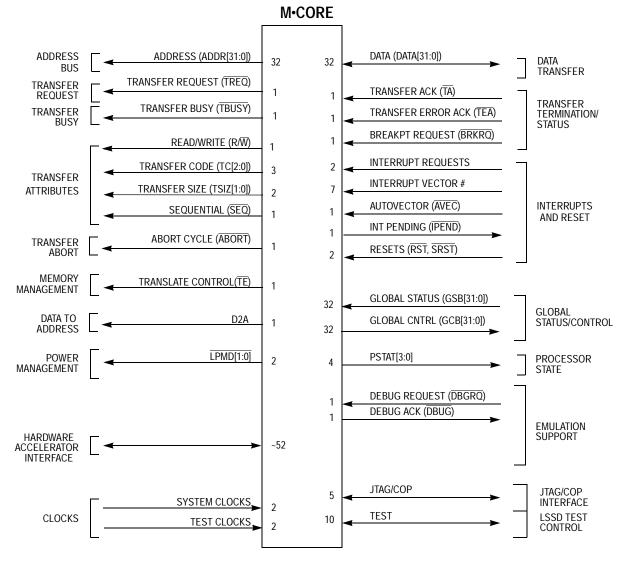

| 5-1   | M•CORE Signal Groups                               | 183  |

| Figur            | re Title                                                | Page |  |

|------------------|---------------------------------------------------------|------|--|

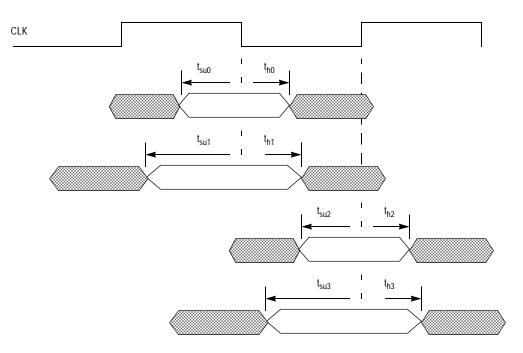

| 6-1              | Signal Relationships to Clocks                          | 197  |  |

| 6-2              | External Multiplexer Connections                        | 198  |  |

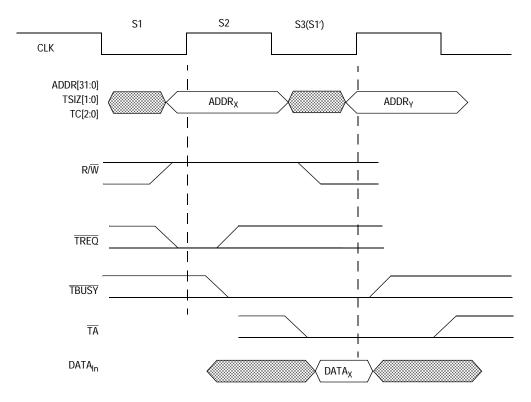

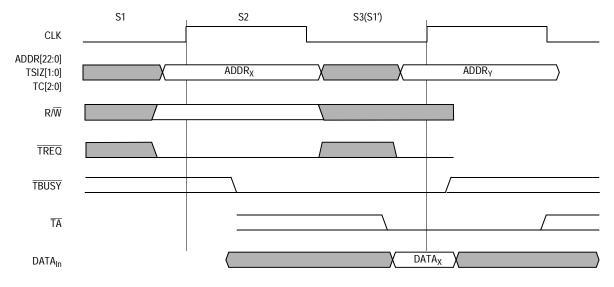

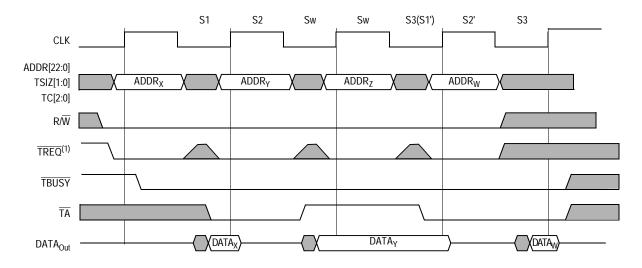

| 6-3              | Instruction/Data Read Cycle                             | 201  |  |

| 6-4              | Read Cycle with Wait States                             | 203  |  |

| 6-5              | Write Cycle                                             | 203  |  |

| 6-6              | Write Cycle with Wait States.                           | 205  |  |

| 6-7              | Data Bus Hand-Off Operation                             | 206  |  |

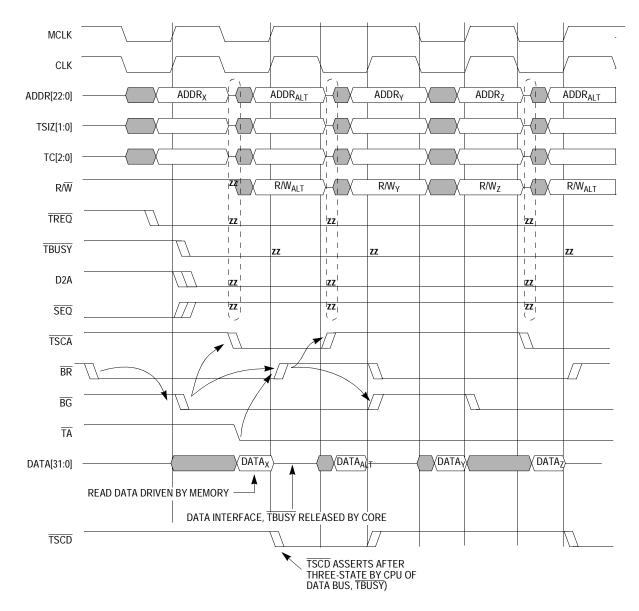

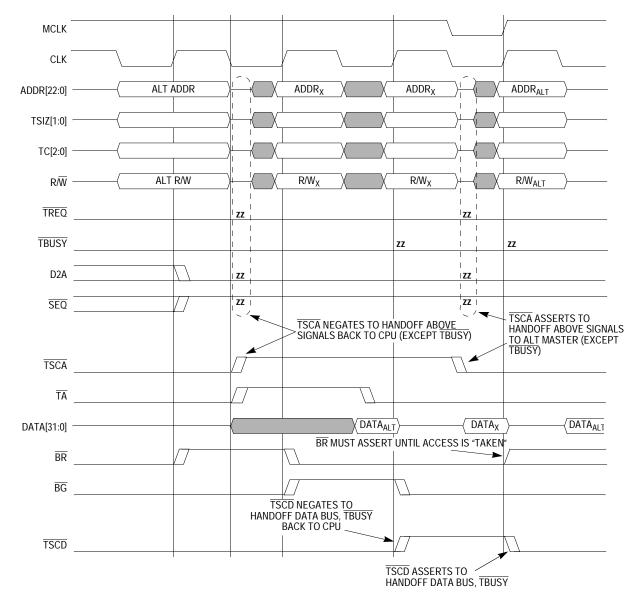

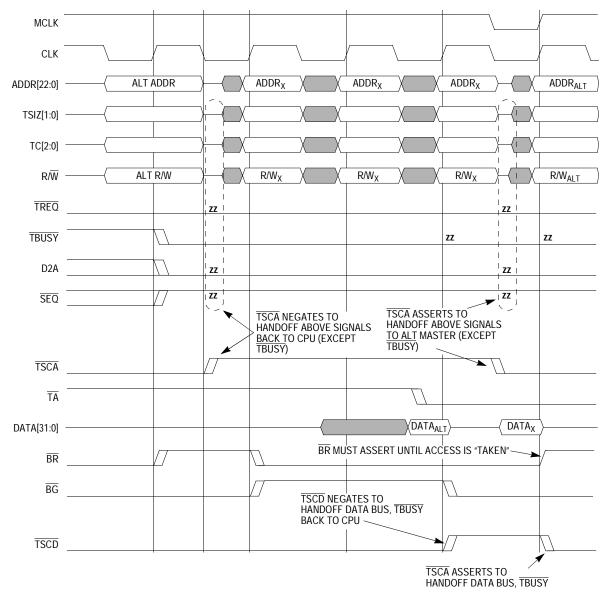

| <mark>6-8</mark> | Data Bus Hand-Off Operation with Wait State             | 207  |  |

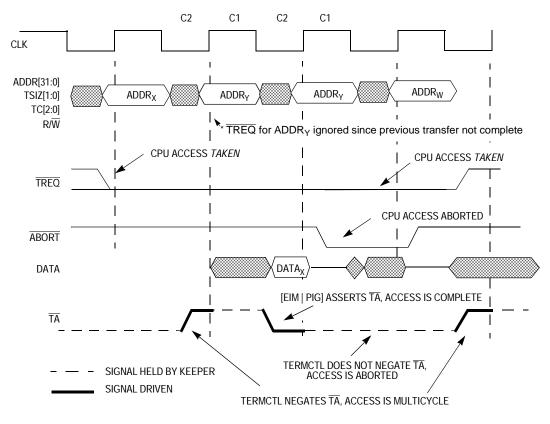

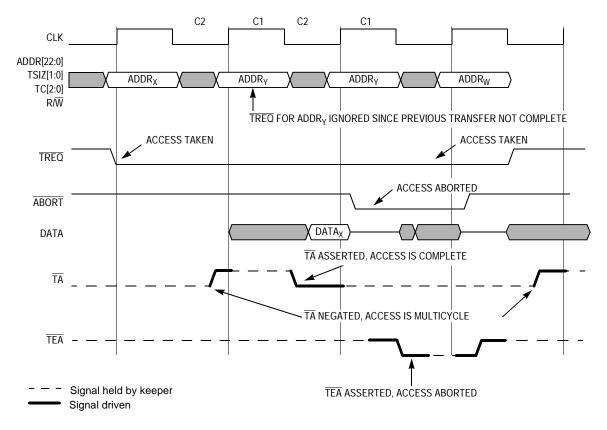

| 6-9              | ABORT Operation.                                        | 209  |  |

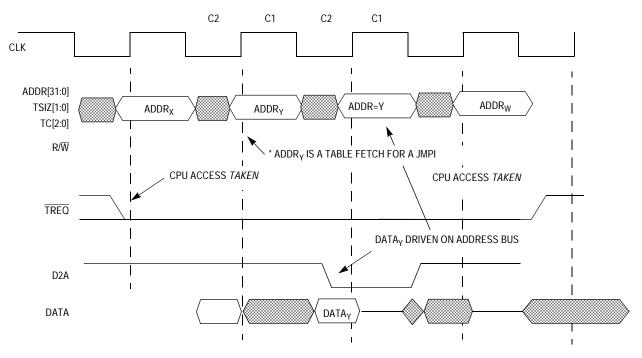

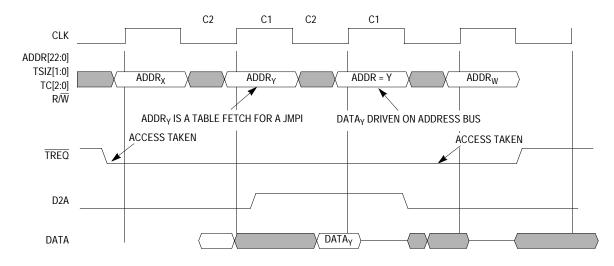

| 6-10             | D2A Operation                                           | 210  |  |

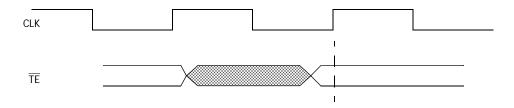

| 6-11             | Translation Control Output                              | 212  |  |

| 6-12             | Interrupt Interface Signals                             | 213  |  |

| 6-13             | Global Status and Control Signals                       | 214  |  |

| 6-14             | Power Management Control Signals (Assertion)            | 216  |  |

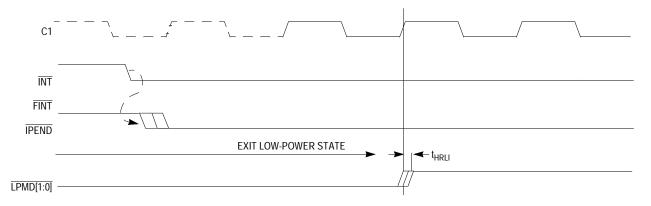

| 6-15             | Power Management Control Signals (Negation)             | 216  |  |

| 6-16             | Debug Request Input Control Signal                      | 217  |  |

| 6-17             | Debug Output Control Signal                             | 217  |  |

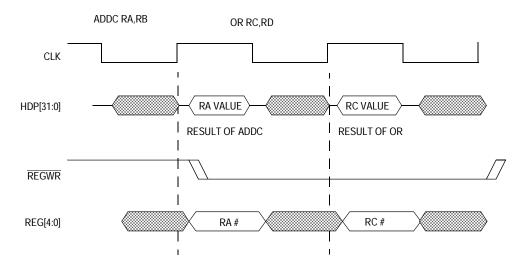

| 7-1              | Register Snoop Operation                                | 222  |  |

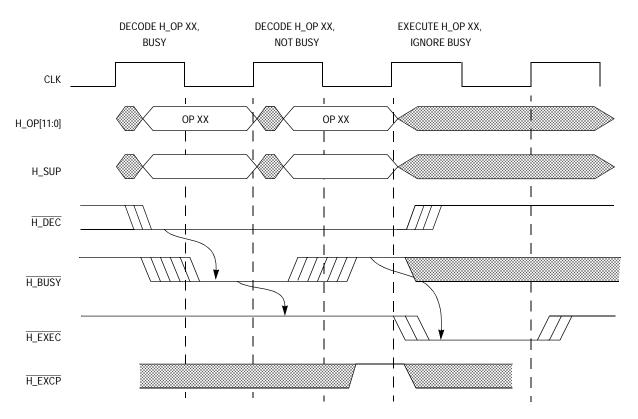

| 7-2              | Basic Instruction Interface                             |      |  |

|                  | Operation, H_BUSY Negated                               | 223  |  |

| 7-3              | Basic Instruction Interface Operation,                  |      |  |

|                  | H_BUSY Asserted                                         | 224  |  |

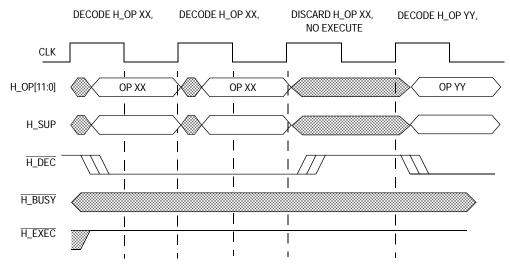

| 7-4              | Instruction Discard                                     | 225  |  |

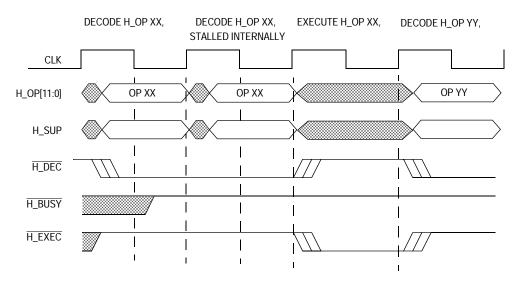

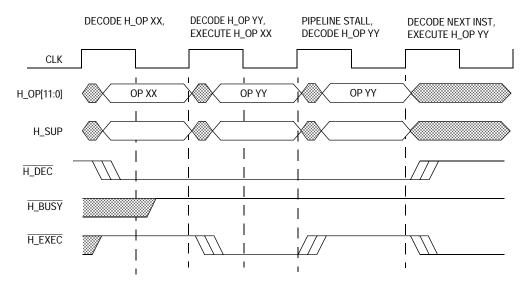

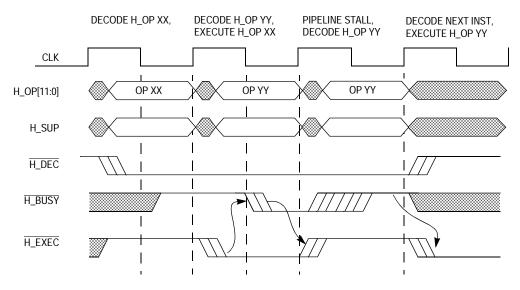

| 7-5              | Instruction Pipeline Stall                              | 226  |  |

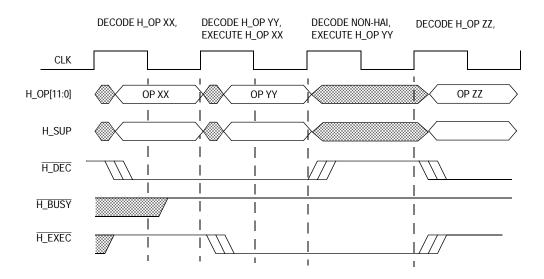

| 7-6              | Back-to-Back HAI Instruction Execution                  | 226  |  |

| 7-7              | Back-to-Back HAI Instruction Execution                  |      |  |

|                  | with Pipeline Stall                                     | 227  |  |

| 7-8              | Back-to-Back HAI Instruction Execution                  | 000  |  |

| 7.0              | with H_BUSY Stall.                                      |      |  |

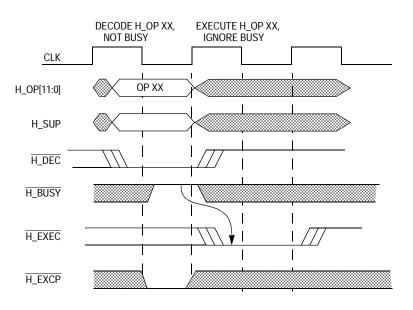

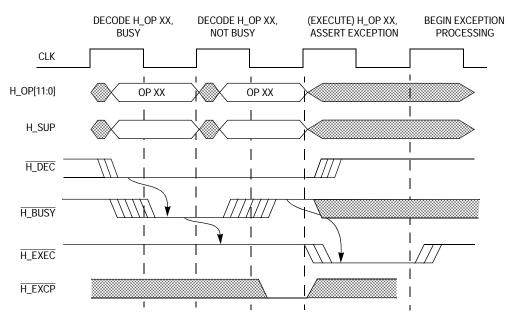

| 7-9              | H_EXCP Operation, H_BUSY Negated                        |      |  |

| 7-10             | H_EXCP Operation, HAI Busy                              |      |  |

| 7-11             | Register Transfers to External Block with Wait State    |      |  |

| 7-12             | Register Transfers from External Block with Wait State. |      |  |

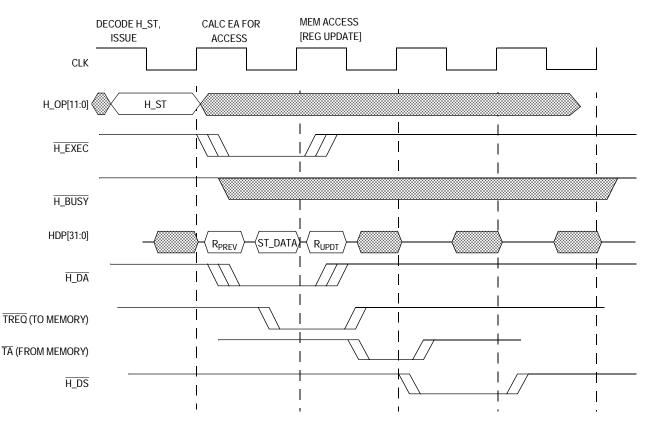

| 7-13             | Memory Transfer to External Block                       | 233  |  |

| Figur | e Title                                                | Page |

|-------|--------------------------------------------------------|------|

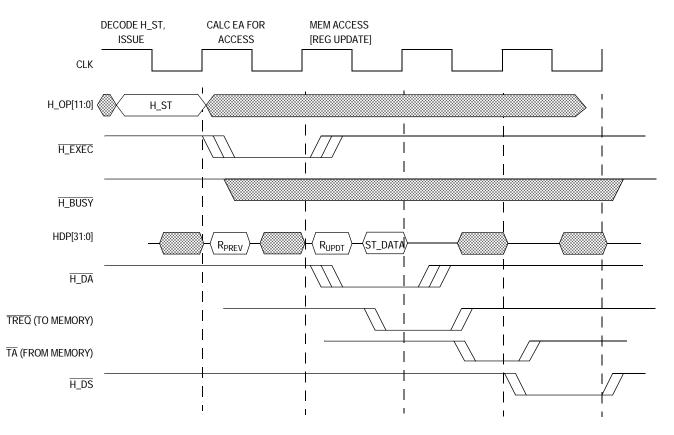

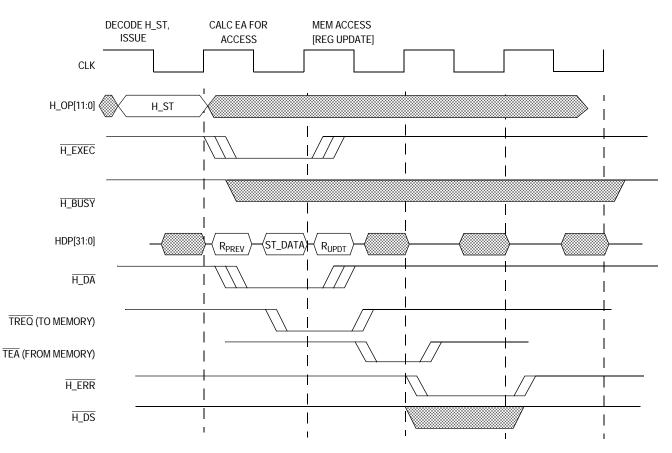

| 7-14  | Memory Transfer to External Block                      |      |

|       | with Access Exception                                  |      |

| 7-15  | Memory Transfer from External Block                    |      |

| 7-16  | Delayed Memory Transfer from External Block            |      |

| 7-17  | Memory Transfer from External Block, Error Termination |      |

| 7-18  | H_CALL Primitive Format.                               |      |

| 7-19  | H_RET Primitive Format.                                |      |

| 7-20  | H_LD Primitive Format                                  |      |

| 7-21  | H_ST Primitive Format                                  |      |

| 7-22  | H_EXEC Primitive Format                                | 241  |

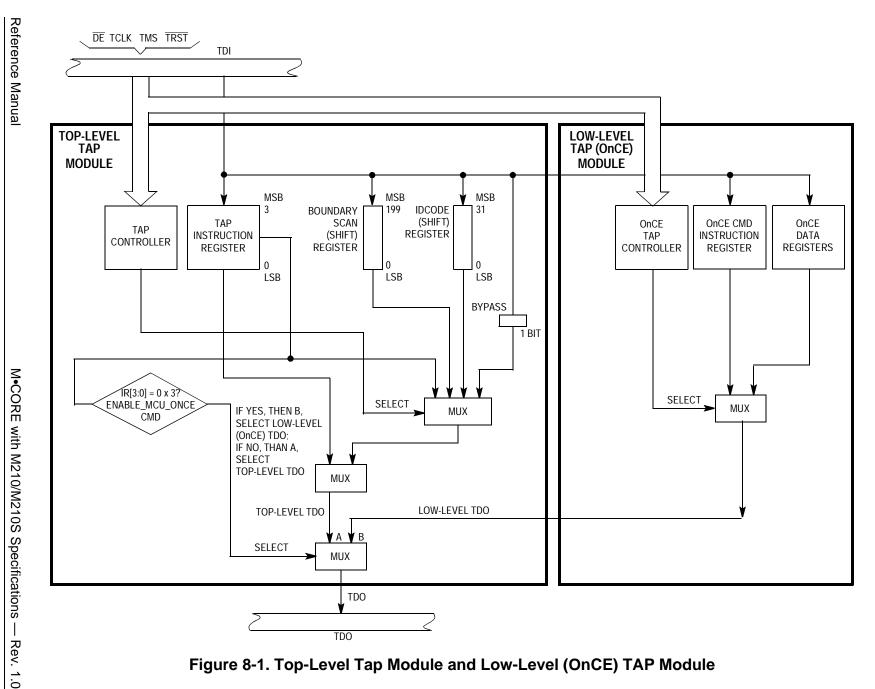

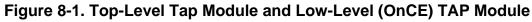

| 8-1   | Top-Level Tap Module and Low-Level (OnCE)              |      |

| 01    | TAP Module                                             | 250  |

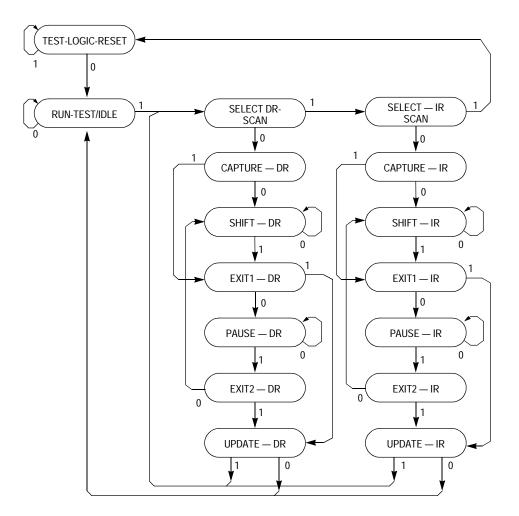

| 8-2   | Top-Level TAP Controller State Machine                 |      |

| 8-3   | IDCODE Register Bit Specification.                     |      |

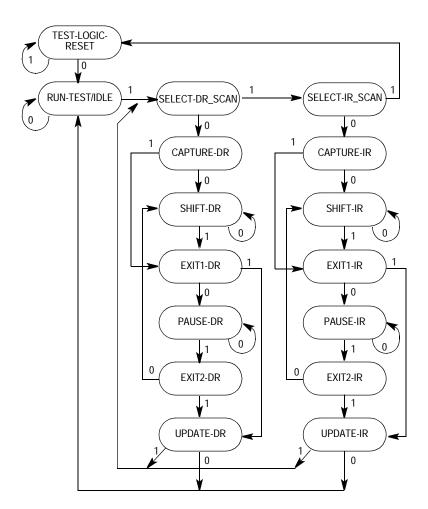

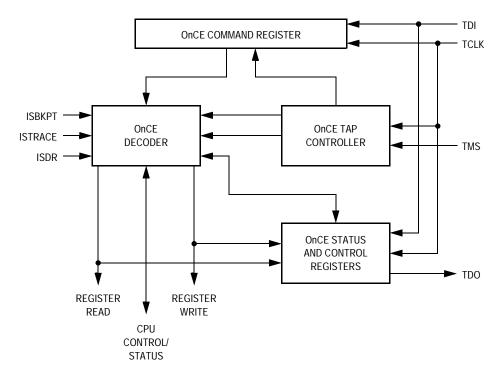

| 8-4   | OnCE Block Diagram                                     |      |

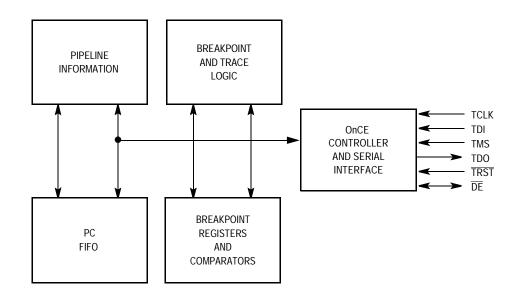

| 8-5   | Low-Level (OnCE) Tap Module Data Registers (DRs)       |      |

| 8-6   | OnCE Controller                                        |      |

| 8-7   | OnCE Controller and Serial Interface                   |      |

| 8-8   | OnCE Command Register (OCMR)                           |      |

| 8-9   | OnCE Control Register (OCR)                            |      |

| 8-10  | OnCE Status Register (OSR)                             |      |

| 8-11  | OnCE Memory Breakpoint Logic                           |      |

| 8-12  | OnCE Trace Logic Block Diagram                         | 287  |

| 8-13  | CPU Scan Chain Register (CPUSCR)                       | 290  |

| 8-14  | Control State Register (CTL)                           | 292  |

| 8-15  | OnCE PC FIFO.                                          |      |

| 8-16  | Recommended Connector Interface                        |      |

|       | to JTAG/OnCE Port                                      | 297  |

| B-1   | Pipeline Stages.                                       | 304  |

| B-2   | Pipeline Flow                                          |      |

|       | •                                                      |      |

| C-1   | M210 Core Interface Signals                            | 311  |

| C-2   | M210S Core Interface Signals                           |      |

|       | -                                                      |      |

| Figur | e Title                                              | Page |

|-------|------------------------------------------------------|------|

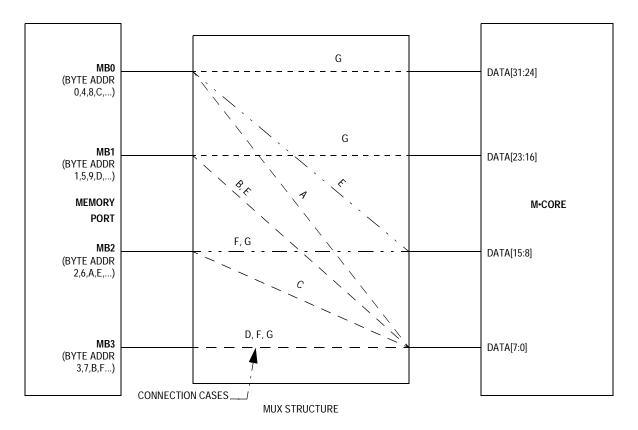

| D-1   | Mux Byte Organization                                | 331  |

| D-2   | Internal Multiplexer Connections                     | 332  |

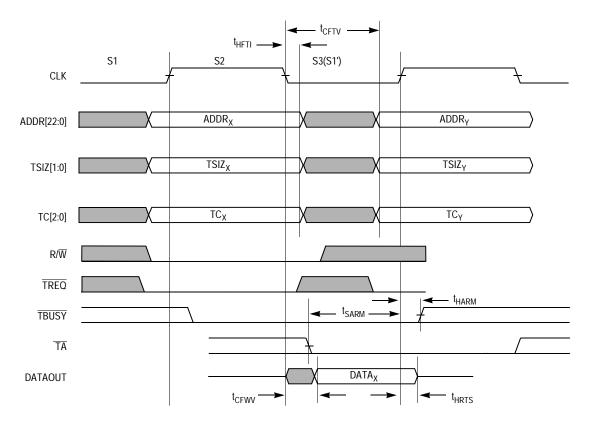

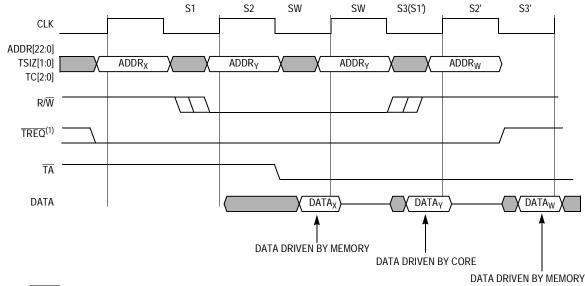

| D-3   | Instruction/Data Read Cycle                          | 334  |

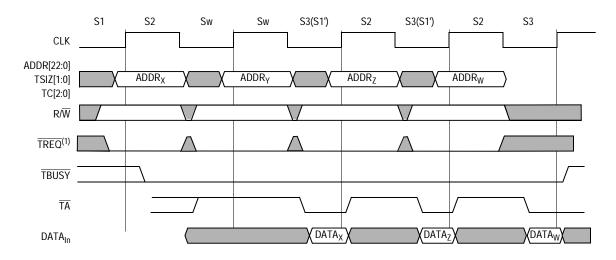

| D-4   | Read Cycle with Wait States                          | 336  |

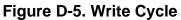

| D-5   | Write Cycle                                          | 337  |

| D-6   | Write Cycle with Wait States.                        | 339  |

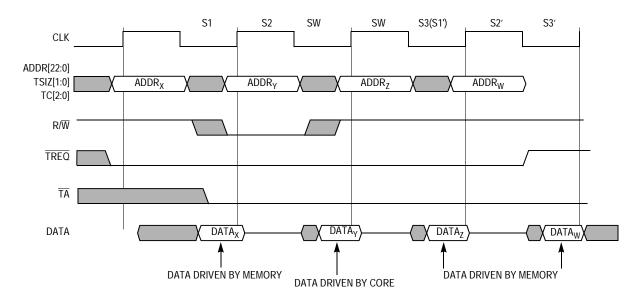

| D-7   | Data Bus Hand-Off Operation.                         | 340  |

| D-8   | Data Bus Hand-Off Operation with Wait State          | 341  |

| D-9   | Combining DATA <sub>In</sub> and DATAO <sub>ut</sub> |      |

|       | Into a Single Bidirectional Data Bus                 | 341  |

| D-10  | Abort Operation                                      | 344  |

| D-11  | Data to Address Transfer                             | 345  |

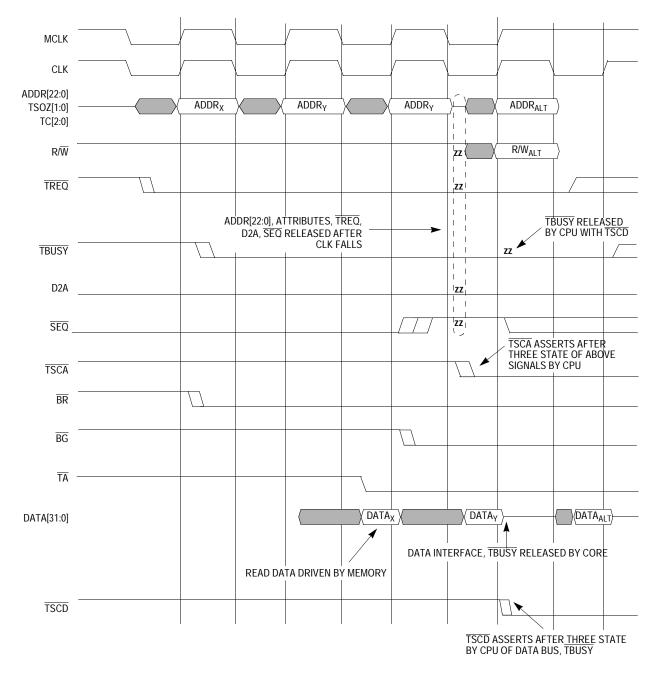

| D-12  | Arbitration Operation, Bus Request $\rightarrow$ Bus |      |

|       | Grant Assertion                                      | 348  |

| D-13  | Arbitration Operation, Bus Request $\rightarrow$ Bus |      |

|       | Grant Assertion, Wait State on Outstanding           |      |

|       | Cycle Before Assertion,                              |      |

|       | Assertion Delayed                                    | 349  |

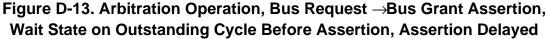

| D-14  | Arbitration Operation, Bus Request $\rightarrow$ Bus |      |

|       | Grant Assertion, Wait State on Outstanding           |      |

|       | Cycle After Assertion                                | 351  |

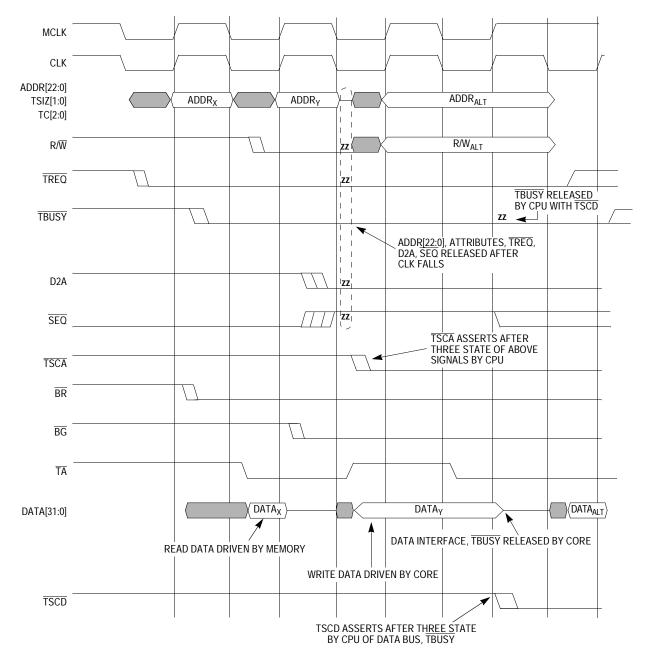

| D-15  | Arbitration Operation, Bus Request $\rightarrow$ Bus |      |

|       | Grant Negation                                       |      |

| D-16  | Arbitration Operation, Back-to-Back Cycles           | 353  |

| D-17  | Arbitration Operation, Bus Request $\rightarrow$ Bus |      |

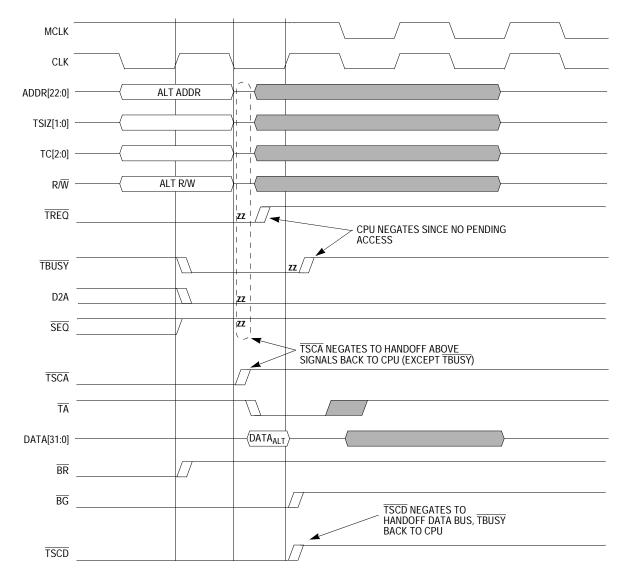

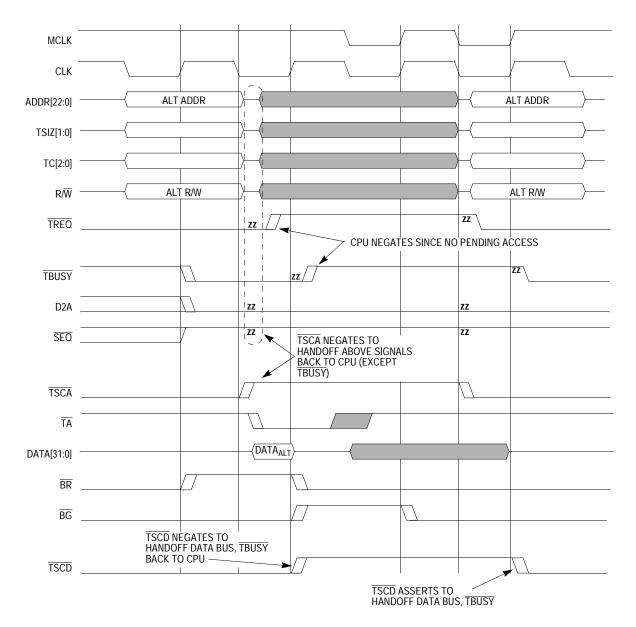

|       | Grant Negation, No Pending CPU Request               | 354  |

| D-18  | Arbitration Operation, Bus Request $\rightarrow$ Bus |      |

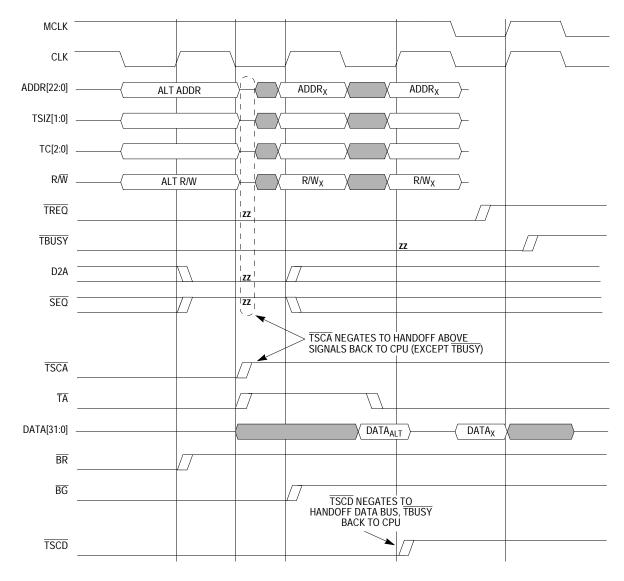

|       | Grant Negation, One Wait State                       |      |

|       | on Alternate Master Cycle                            | 355  |

| D-19  | Arbitration Operation, Bus Request $\rightarrow$ Bus |      |

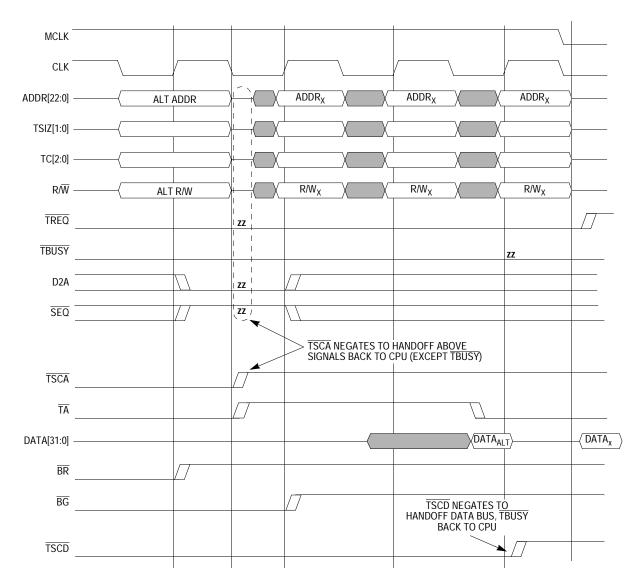

|       | Grant Negation, Multiple Wait States                 |      |

|       | on Alternate Master Cycle                            | 356  |

| D-20  | Bus Re-request with Wait State                       |      |

|       | on Alternate Master Cycle                            | 357  |

| D-21  | Bus Re-request with Multiple Wait States             |      |

|       | on Alternate Master Cycle                            | 358  |

|       |                                                      |      |

| Figur | e Title                                                                            | Page |

|-------|------------------------------------------------------------------------------------|------|

| D-22  | Arbitration Operation, Bus Request →Bus<br>Grant Negation, No Pending CPU Request, |      |

|       | Bus Re-Request                                                                     | 359  |

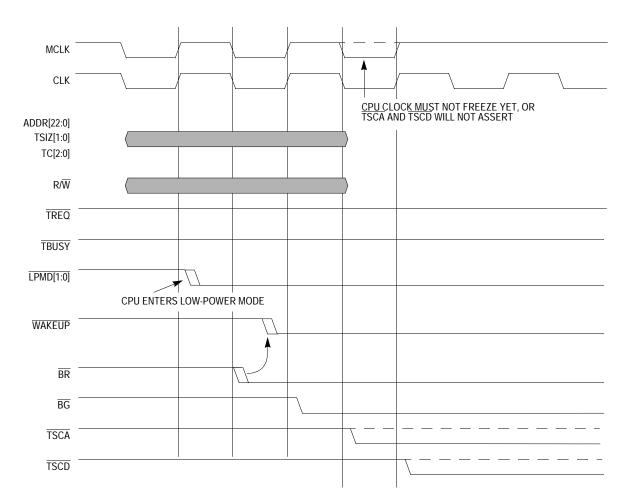

| D-23  | Arbitration Operation, Entry into Low-Power Mode                                   | 361  |

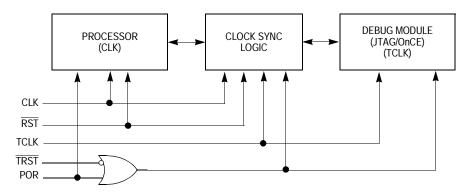

| D-24  | M210 Clocks and Reset Domains                                                      | 362  |

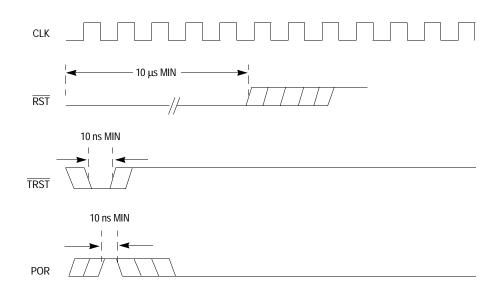

| D-25  | Reset Timing Requirements                                                          | 364  |

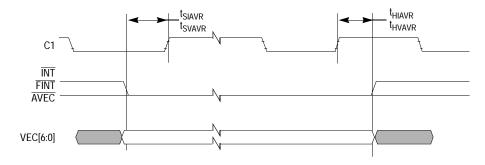

| D-26  | Interrupt Interface Signals                                                        | 365  |

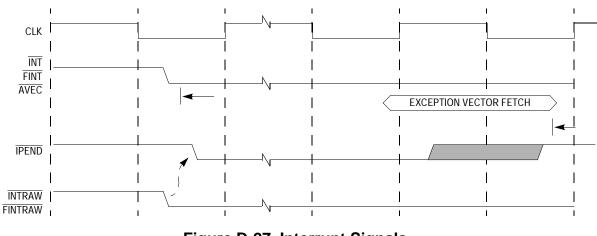

| D-27  | Interrupt Signals                                                                  |      |

| D-28  | Global Status and Control Signals                                                  | 367  |

| D-29  | Power Management Signals Assertion                                                 | 368  |

| D-30  | Power Management Signals Negation                                                  | 368  |

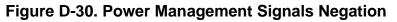

| D-31  | Wakeup Control Signal (WAKEUP)                                                     | 369  |

## Reference Manual — M•CORE with M210/M210S Specifications

# **List of Tables**

| Table | e Title                                          | Page |

|-------|--------------------------------------------------|------|

| 1-1   | M•CORE Instruction Set                           |      |

| 3-1   | Monadic Instructions                             |      |

| 3-2   | Dyadic Instructions                              | 56   |

| 3-3   | 5-Bit Immediate Instructions                     |      |

| 3-4   | 5-Bit Offset Immediate Instructions              |      |

| 3-5   | Opcode Map                                       | 63   |

| 4-1   | Exception Vector Assignments                     | 167  |

| 4-2   | Exception Priority Groups                        |      |

| 4-3   | Exceptions, Tracing, and BRKRQ Results           | 178  |

| 5-1   | Signal Index                                     | 183  |

| 5-2   | Transfer Code Encoding.                          | 186  |

| 5-3   | TSIZx Encoding                                   | 186  |

| 5-4   | LPMD[1:0]   Encoding.                            | 190  |

| 5-5   | PSTATx Encoding                                  | 191  |

| 5-6   | Signal Summary                                   | 194  |

| 6-1   | Interface Requirements for Read and Write Cycles |      |

| 6-2   | Termination Result Summary                       | 207  |

| 8-1   | JTAG Instructions                                |      |

| 8-2   | List of Pins Not Scanned in JTAG Mode            |      |

| 8-3   | Boundary-Scan Register Definition.               |      |

| 8-4   | OnCE Register Addressing                         |      |

| 8-5   | Sequential Control Field Settings                |      |

| 8-6   | Memory Breakpoint Control Field Settings         |      |

| 8-7   | Processor Mode Field Settings                    | 283  |

| M•CORE with M210/M210S Sp | pecifications — Rev. 1.0 |

|---------------------------|--------------------------|

|---------------------------|--------------------------|

**Reference Manual**

| Table                                  | Title                                                                                                                                                                              | Page                     |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| A-1                                    | Symbols and Operators                                                                                                                                                              | 300                      |

| B-1                                    | Instruction Execution Time                                                                                                                                                         | 305                      |

| C-1<br>C-2<br>C-3<br>C-4<br>C-5<br>C-6 | M210/M210S Signal Descriptions.<br>M210/M210S Signal Characteristics.<br>Transfer Code Encoding.<br>Transfer Size Encoding<br>Processor Status Encoding<br>Low-Power Mode Encoding | 315<br>319<br>320<br>321 |

| D-1<br>D-2<br>D-3<br>D-4               | Interface Requirements for Read and Write CyclesTermination Result SummaryM210 Reset and Clock DomainsReset Signals                                                                | 342<br>362               |

# **Section 1. Overview**

#### 1.1 Contents

| 1.2 | Introduction                    |

|-----|---------------------------------|

| 1.3 | Features                        |

| 1.4 | Microarchitecture Summary       |

| 1.5 | Programming Model               |

| 1.6 | Data Format Summary             |

| 1.7 | Operand Addressing Capabilities |

| 1.8 | Instruction Set Overview        |

#### **1.2 Introduction**

The 32-bit M•CORE microRISC engine represents a new line of Motorola microprocessor core products. The processor architecture has been designed for high-performance and cost-sensitive embedded control applications, with particular emphasis on reduced system power consumption. This makes the M•CORE suitable for battery-operated, portable products, as well as for highly integrated parts designed for a high temperature environment.

Total system power consumption is dictated by various components in addition to the processor core. In particular, memory power consumption (both on-chip and external) is expected to dominate overall power consumption of the core-plus-memory subsystem. With this factor in mind, the instruction set architecture (ISA) for M•CORE makes the trade-off of absolute performance capability versus total energy consumption in favor of reducing the overall energy consumption, while maintaining an acceptably high level of performance at a given clock frequency.

#### Overview

The M•CORE is a streamlined execution engine that provides many of the same performance enhancements as mainstream reduced instruction set computer (RISC) designs. Fixed length instruction encodings and a strict load/store architecture minimize control complexity and overhead. The goal of minimizing the overhead of memory system energy consumption is achieved by adopting a (relatively) short 16-bit instruction encoding. This choice significantly lowers the memory bandwidth needed to sustain a high rate of instruction execution.

Code density statistics for a number of applications show relative code density competitive in comparison to complex instruction set computer (CISC) designs, and implementation statistics show a large reduction in complexity and overhead relative to a CISC approach.

In addition to substantial cost and performance benefits, M•CORE also offers advantages in power consumption and power management. M•CORE minimizes power dissipation by using a fully static design, dynamic power management, and low-voltage operation. The M•CORE automatically powers down internal functional blocks that are not needed on a clock-by-clock basis. Power conservation modes are also provided for absolute power conservation on a coarser granularity.

#### **1.3 Features**

The main features of the M•CORE are:

- 32-bit load/store RISC architecture

- Fixed 16-bit instruction length

- 16-entry 32-bit general-purpose register file

- Efficient 4-stage execution pipeline, hidden from application software

- Single-cycle instruction execution for many instructions

- Two cycles for branches and memory access instructions

- Support for byte, half-word, and word memory accesses

- Fast interrupt support with 16-entry dedicated alternate register file

- Vectored and autovectored interrupt support

#### **1.4 Microarchitecture Summary**

The M•CORE instruction execution pipeline consists of these stages:

- Instruction fetch

- Instruction decode/register file read

- Execute

- Register writeback

These stages operate in an overlapped fashion, allowing single clock instruction execution for most instructions.

Sixteen general-purpose registers are provided for source operands and instruction results. Register R15 is used as the link register to hold the return address for subroutine calls, and register R0 is associated with the current stack pointer value by convention.

The execution unit consists of:

- 32-bit arithmetic/logic unit (ALU)

- 32-bit barrel shifter

- Find-first-one unit (FFO)

- Result feed-forward hardware

- Miscellaneous support hardware for multiplication and multiple register loads and stores

Arithmetic and logical operations are executed in a single cycle with the exception of the multiply, signed divide, and unsigned divide instructions. The multiply instruction is implemented with a 2-bit per clock, overlapped-scan, modified Booth algorithm with early-out capability to reduce execution time for operations with small multiplier values. The signed divide and unsigned divide instructions also have

data-dependent timing. A find-first-one unit operates in a single clock cycle.

The program counter unit has a PC incrementer and a dedicated branch address adder to minimize delays during change of flow operations. Branch target addresses are calculated in parallel with branch instruction decode, with a single pipeline bubble for taken branches and jumps. This results in an execution time of two clocks. Conditional branches that are not taken execute in a single clock.

Memory load and store operations are provided for byte, half-word, and word (32-bit) data with automatic zero extension of byte and half-word load data. These instructions can execute in two clock cycles. Load and store multiple register instructions allow low overhead context save and restore operations. These instructions can execute in (N + 1) clock cycles, where N is the numbers of registers to transfer.

A single condition code/carry (C) bit is provided for condition testing and for use in implementing arithmetic and logical operations greater than 32 bits. Typically, the C bit is set only by explicit test/comparison operations, not as a side-effect of normal instruction operation. Exceptions to this rule occur for specialized operations for which it is desirable to combine condition setting with actual computation.

A 16-entry alternate register file is provided to support low overhead interrupt exception processing. The CPU supports both vectored and autovectored interrupts.

#### 1.5 Programming Model

The M•CORE programming model is defined separately for two privilege modes: supervisor and user. Certain operations are not available in user mode.

User programs can only access registers specific to the user mode; system software executing in the supervisor mode can access all registers, using the control registers to perform supervisory functions. User programs are thus restricted from accessing privileged information.

**Reference Manual**

The operating system performs management and service tasks for the user programs by coordinating their activities.

Most instructions execute in either mode, but some instructions that have important system effects are privileged and can only execute in the supervisor mode. For instance, user programs cannot execute the STOP, DOZE, or WAIT instructions. To prevent a user program from entering the supervisor mode except in a controlled manner, instructions that can alter the S-bit in the program status register (PSR) are privileged. The TRAP #N instructions provide controlled access to operating system services for user programs. Access to special control registers is also precluded in user mode.

When the S bit in the PSR is set, the processor executes instructions in the supervisor mode. Bus cycles associated with an instruction indicate either supervisor or user access depending on the mode.

The processor uses the user programming model during normal user mode processing. During exception processing, the processor changes from user to supervisor mode. Exception processing saves the current value of the PSR in the EPSR or FPSR shadow control register and then sets the S bit in the PSR, forcing the processor into the supervisor mode. To return to the previous operating mode, a system routine may execute the RTE (return from exception) or RFI (return from fast interrupt) instruction as appropriate, causing the instruction pipeline to be flushed and refilled from the appropriate address space.

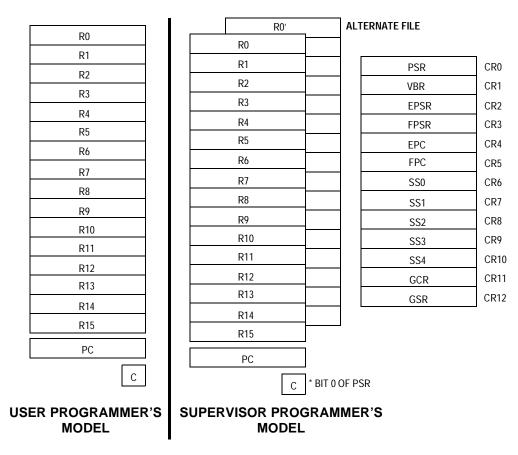

The registers depicted in the programming model (see **Figure 1-1**) provide operand storage and control. The registers are partitioned into two levels of privilege: user and supervisor. The user programming model consists of:

- 16 general-purpose 32-bit registers

- 32-bit program counter (PC)

- Condition/carry (C) bit

The C bit is implemented as bit 0 of the PSR. This is the only portion of the PSR accessible by the user. The supervisor programming model consists of sixteen additional 32-bit general-purpose registers (the alternate file), as well as a set of status/control registers and scratch

registers. By convention, register R15 serves as the link register for subroutine calls, and register R0 is typically used as the current stack pointer.

The alternate file is selected for use via a control bit in the PSR. The status, control, and scratch registers are accessed via the move-fromcontrol register (MFCR) and move-to-control register (MTCR) instructions. When the alternate file is selected via the AF bit in the PSR, general-purpose operands are accessed from it. When the AF bit is cleared, operands are accessed from the normal file. This alternate file is provided to allow very low overhead context switching capability for real-time event handling.

Figure 1-1. Programming Model

32

The supervisor programming model includes the PSR, which contains operation control and status information. In addition, a set of exception shadow registers are provided to save the state of the PSR and the program counter at the time an exception occurs. A separate set of shadow registers is provided for fast interrupt support to minimize context saving overhead.

Five scratch registers are provided for supervisor software use in handling exception events. A single register is provided to alter the base address of the exception vector table. Two registers are provided for global control and status.

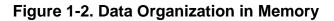

#### **1.6 Data Format Summary**

The operand data formats supported by the integer unit are standard two's-complement data formats. The operand size for each instruction is either explicitly encoded in the instruction (load/store instructions) or implicitly defined by the instruction operation (index operations, byte extraction). Typically, instructions operate on all 32 bits of the source operand(s) and generate a 32-bit result.

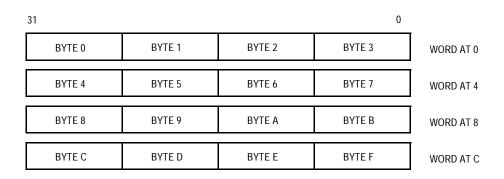

Memory is viewed from a big-endian byte ordering perspective. The most significant byte (byte 0) of word 0 is located at address 0. Bits are numbered within a word starting with bit 31 as the most significant bit.

Figure 1-3. Data Organization in Registers

#### 1.7 Operand Addressing Capabilities

M•CORE accesses all memory operands through load and store instructions, transferring data between the general-purpose registers and memory. Register-plus-four-bit scaled displacement addressing mode is used for the load and store instructions to address byte, halfword, or word (32-bit) data.

Load and store multiple instructions allow a subset of the 16 generalpurpose registers to be transferred to or from a base address pointed to by register R0 (the default stack pointer by convention).

Load and store register quadrant instructions use register indirect addressing to transfer a register quadrant to or from memory.

#### **1.8 Instruction Set Overview**

The instruction set is tailored to support high-level languages and is optimized for those instructions most commonly executed. A standard set of arithmetic and logical instructions is provided, as well as instruction support for bit operations, byte extraction, data movement, control flow modification, and a small set of conditionally executed

**Reference Manual**

instructions which can be useful in eliminating short conditional branches.

**Table 1-1** is an alphabetized listing of the M•CORE instruction set. Refer to **Section 3. Instructions** for more details on instruction operation.

| Mnemonic | Description                                                      |

|----------|------------------------------------------------------------------|

| ABS      | Absolute Value                                                   |

| ADDC     | Add with C bit                                                   |

| ADDI     | Add Immediate                                                    |

| ADDU     | Add Unsigned                                                     |

| AND      | Logical AND                                                      |

| ANDI     | Logical AND Immediate                                            |

| ANDN     | AND NOT                                                          |

| ASR      | Arithmetic Shift Right                                           |

| ASRI     | Arithmetic Shift Right Immediate                                 |

| ASRC     | Arithmetic Shift Right, Update C Bit                             |

| BCLRI    | Clear Bit                                                        |

| BF       | Branch on Condition False                                        |

| BGENI    | Bit Generate Immediate                                           |

| BGENR    | Bit Generate Register                                            |

| BKPT     | Breakpoint                                                       |

| BMASKI   | Bit Mask Immediate                                               |

| BR       | Branch                                                           |

| BREV     | Bit Reverse                                                      |

| BSETI    | Bit Set Immediate                                                |

| BSR      | Branch to Subroutine                                             |

| BT       | Branch on Condition True                                         |

| BTSTI    | Bit Test Immediate                                               |

| CLRF     | Clear Register on Condition False                                |

| CLRT     | Clear Register on Condition True                                 |

| CMPHS    | Compare Higher or Same                                           |

| CMPLT    | Compare Less Than                                                |

| CMPLTI   | Compare Less Than Immediate                                      |

| CMPNE    | Compare Not Equal                                                |

| CMPNEI   | Compare Not Equal Immediate                                      |

| DECF     | Decrement on Condition False                                     |

| DECGT    | Decrement Register and Set Condition if Result Greater Than Zero |

| DECLT    | Decrement Register and Set Condition if Result Less Than Zero    |

| DECNE    | Decrement Register and Set Condition if Result Not Equal to Zero |

| DECT     | Decrement on Condition True                                      |

| DIVS     | Divide (Signed)                                                  |

| DIVU     | Divide (Unsigned)                                                |

| DOZE     | Doze                                                             |

Table 1-1. M•CORE Instruction Set (Sheet 1 of 3)

M•CORE with M210/M210S Specifications — Rev. 1.0

**Reference Manual**

| Mnemonic   | Description                                              |

|------------|----------------------------------------------------------|

| FF1        | Find First One                                           |

| INCF       | Increment on Condition False                             |

| INCT       | Increment on Condition True                              |

| IXH        | Index Half-Word                                          |

| IXW        | Index Word                                               |

| JMP        | Jump                                                     |

| JMPI       | Jump Indirect                                            |

| JSR        | Jump to Subroutine                                       |

| JSRI       | Jump to Subroutine Indirect                              |

| LD.[BHW]   | Load                                                     |

| LDM        | Load Multiple Registers                                  |

| LDQ        | Load Register Quadrant                                   |

| LOOPT      | Decrement with C-Bit Update and Branch if Condition True |

| LRW        | Load Relative Word                                       |

| LSL, LSR   | Logical Shift Left and Right                             |

| LSLC, LSRC | Logical Shift Left and Right, Update C Bit               |

| LSLI, LSRI | Logical Shift Left and Right by Immediate                |

| MFCR       | Move from Control Register                               |

| MOV        | Move                                                     |

| MOVI       | Move Immediate                                           |

| MOVF       | Move on Condition False                                  |

| MOVT       | Move on Condition True                                   |

| MTCR       | Move to Control Register                                 |

| MULT       | Multiply                                                 |

| MVC        | Move C Bit to Register                                   |

| MVCV       | Move Inverted C Bit to Register                          |

| NOT        | Logical Complement                                       |

| OR         | Logical Inclusive-OR                                     |

| ROTLI      | Rotate Left by Immediate                                 |

| RSUB       | Reverse Subtract                                         |

| RSUBI      | Reverse Subtract Immediate                               |

| RTE        | Return from Exception                                    |

| RFI        | Return from Interrupt                                    |

| SEXTB      | Sign-Extend Byte                                         |

| SEXTH      | Sign-Extend Half-word                                    |

| ST.[BHW]   | Store                                                    |

| STM        | Store Multiple Registers                                 |

| STQ        | Store Register Quadrant                                  |

| STOP       | Stop                                                     |

| SUBC       | Subtract with C Bit                                      |

| SUBU       | Subtract                                                 |

| SUBI       | Subtract                                                 |

| SUBI       | Subtract Immediate                                       |

| SYNC       | Synchronize                                              |

| Table 1-1. M•CORE Instruction Set (Sh | heet 2 of 3) |

|---------------------------------------|--------------|

|---------------------------------------|--------------|

| Mnemonic | Description                 |

|----------|-----------------------------|

| TRAP     | Trap                        |

| TST      | Test Operands               |

| TSTNBZ   | Test for No Byte Equal Zero |

| WAIT     | Wait                        |

| XOR      | Exclusive OR                |

| XSR      | Extended Shift Right        |

| XTRB0    | Extract Byte 0              |

| XTRB1    | Extract Byte 1              |

| XTRB2    | Extract Byte 2              |

| XTRB3    | Extract Byte 3              |

| ZEXTB    | Zero-Extend Byte            |

| ZEXTH    | Zero-Extend Half-Word       |

# Overview

38

# **Section 2. Registers**

# 2.1 Contents

| 2.2     | Introduction                                      |

|---------|---------------------------------------------------|

| 2.3     | User Programming Model40                          |

| 2.3.1   | General-Purpose Registers41                       |

| 2.3.2   | Program Counter                                   |

| 2.3.3   | Condition Code/Carry Bit41                        |

| 2.4     | Supervisor Programming Model                      |

| 2.4.1   | Alternate Register File43                         |

| 2.4.2   | Processor Status Register43                       |

| 2.4.2.  | 1 Updates to the PSR48                            |

| 2.4.2.2 | 2 Exception Recognition and Processing Updates 48 |

| 2.4.2.3 | 3 RTE and RFI Instruction Updates                 |

| 2.4.2.4 | 4 MTCR Instruction Updates                        |

| 2.4.3   | Vector Base Register                              |

| 2.4.4   | Supervisor Storage Registers                      |

| 2.4.5   | Exception Shadow Registers                        |

| 2.4.6   | Global Control Register51                         |

| 2.4.7   | Global Status Register                            |

|         |                                                   |

# 2.2 Introduction

This section describes the organization of the M•CORE general-purpose registers (GPRs) and control registers in the user and supervisor programming models. Refer to **Section 4. Exception Processing** for details on the exception model.

# 2.3 User Programming Model

The user programming model's register usage, as proposed by the *Motorola Applications Binary Interface Standard* (Motorola document number MCOREABISM/AD) and shown in **Figure 2-1**, consists of these registers and the described uses:

- 16 general-purpose 32-bit registers (R[0:15])

- 32-bit program counter (PC)

- Condition code/carry flag (C bit)

| R0STACK POINTERR1SCRATCHR2FIRST ARGUMENTR3SECOND ARGUMENTR4THIRD ARGUMENTR5FOURTH ARGUMENTR6FIFTH ARGUMENTR7SIXTH ARGUMENTR8LOCALR9LOCALR10LOCALR12LOCALR13LOCALR14LOCALR15LINK/SCRATCHPCPROGRAM COUNTER |     |                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|

| R2FIRST ARGUMENTR3SECOND ARGUMENTR4THIRD ARGUMENTR5FOURTH ARGUMENTR6FIFTH ARGUMENTR7SIXTH ARGUMENTR8LOCALR9LOCALR10LOCALR11LOCALR12LOCALR13LOCALR14LOCALR15LINK/SCRATCH                                  | R0  | STACK POINTER   |

| R3SECOND ARGUMENTR4THIRD ARGUMENTR5FOURTH ARGUMENTR6FIFTH ARGUMENTR7SIXTH ARGUMENTR8LOCALR9LOCALR10LOCALR11LOCALR12LOCALR13LOCALR14LOCALR15LINK/SCRATCHPCPROGRAM COUNTER                                 | R1  | SCRATCH         |

| R4THIRD ARGUMENTR5FOURTH ARGUMENTR6FIFTH ARGUMENTR7SIXTH ARGUMENTR8LOCALR9LOCALR10LOCALR11LOCALR12LOCALR13LOCALR14LOCALR15LINK/SCRATCHPCPROGRAM COUNTER                                                  | R2  | FIRST ARGUMENT  |

| R5FOURTH ARGUMENTR6FIFTH ARGUMENTR7SIXTH ARGUMENTR8LOCALR9LOCALR10LOCALR11LOCALR12LOCALR13LOCALR14LOCALR15LINK/SCRATCHPCPROGRAM COUNTER                                                                  | R3  | SECOND ARGUMENT |

| R6FIFTH ARGUMENTR7SIXTH ARGUMENTR8LOCALR9LOCALR10LOCALR11LOCALR12LOCALR13LOCALR14LOCALR15LINK/SCRATCHPCPROGRAM COUNTER                                                                                   | R4  | THIRD ARGUMENT  |

| R7SIXTH ARGUMENTR8LOCALR9LOCALR10LOCALR11LOCALR12LOCALR13LOCALR14LOCALR15LINK/SCRATCHPCPROGRAM COUNTER                                                                                                   | R5  | FOURTH ARGUMENT |

| R8LOCALR9LOCALR10LOCALR11LOCALR12LOCALR13LOCALR14LOCALR15LINK/SCRATCHPCPROGRAM COUNTER                                                                                                                   | R6  | FIFTH ARGUMENT  |

| R9LOCALR10LOCALR11LOCALR12LOCALR13LOCALR14LOCALR15LINK/SCRATCHPCPROGRAM COUNTER                                                                                                                          | R7  | SIXTH ARGUMENT  |

| R10     LOCAL       R11     LOCAL       R12     LOCAL       R13     LOCAL       R14     LOCAL       R15     LINK/SCRATCH       PC     PROGRAM COUNTER                                                    | R8  | LOCAL           |

| R11     LOCAL       R12     LOCAL       R13     LOCAL       R14     LOCAL       R15     LINK/SCRATCH       PC     PROGRAM COUNTER                                                                        | R9  | LOCAL           |

| R12     LOCAL       R13     LOCAL       R14     LOCAL       R15     LINK/SCRATCH       PC     PROGRAM COUNTER                                                                                            | R10 | LOCAL           |

| R12     LOCAL       R14     LOCAL       R15     LINK/SCRATCH       PC     PROGRAM COUNTER                                                                                                                | R11 | LOCAL           |

| R14     LOCAL       R15     LINK/SCRATCH       PC     PROGRAM COUNTER                                                                                                                                    | R12 | LOCAL           |

| R15 LINK/SCRATCH<br>PC PROGRAM COUNTER                                                                                                                                                                   | R13 | LOCAL           |

| PC PROGRAM COUNTER                                                                                                                                                                                       | R14 | LOCAL           |

|                                                                                                                                                                                                          | R15 | LINK/SCRATCH    |

| С                                                                                                                                                                                                        | PC  | PROGRAM COUNTER |

|                                                                                                                                                                                                          | C   |                 |

Figure 2-1. User Programming Model

The registers with local usage, as well as R0 (stack pointer), are preserved (by conforming compliers) during a function call. The contents of the argument and scratch registers must be saved by the calling routine if they are to be preserved. More detail about standard register usage can be found in the M•CORE ABI manual cited above.

**Reference Manual**

#### 2.3.1 General-Purpose Registers

The general-purpose registers contain instruction operands and results, and provide address information as well. Software and hardware register conventions have been established for subroutine linkage, parameter passing, and for a stack pointer.

#### 2.3.2 Program Counter

The program counter (PC) contains the address of the currently executing instruction. During instruction execution and exception processing, the processor automatically increments the PC value or places a new value in the PC, as appropriate. For some instructions, the PC can be used as a pointer for PC-relative addressing. The low order bit of the PC is always forced to 0.

#### 2.3.3 Condition Code/Carry Bit

The condition code/carry (C) bit represents a condition generated by a processor operation. The C bit can be set explicitly by comparison operations or implicitly as a result of executing extended precision arithmetic and logical operations. In addition, specialized instructions (such as the decrement, loop, and extract byte instructions) update the C bit as a result of normal execution.

# 2.4 Supervisor Programming Model

System programmers use the supervisor programming model to implement sensitive operating system functions, input/output (I/O) control, and privileged operations.

# Registers

The supervisor programming model consists of the registers available to the user as well as these registers (see Figure 2-2):

- 16-entry, 32-bit alternate register file

- Processor status register (PSR)

- Vector base register (VBR)

- Exception saved PSR (EPSR)

- Fast interrupt saved PSR (FPSR)

- Exception saved program counter (EPC)

- Fast interrupt saved program counter (FPC)

- Five 32-bit supervisor scratch registers (SS0–SS4)

- 32-bit global control register (GCR)

- 32-bit global status register (GSR)

| R0′            |

|----------------|

| R1′            |

| R2′            |

| R3′            |

| R4′            |

| R5′            |

| R6′            |

| R7′            |

| R8′            |

| R9′            |

| R10′           |

| R11′           |

| R12'           |

| R13′           |

| R14′           |

| R15′           |

| ALTERNATE FILE |

|                |

| PSR  | CR0  |

|------|------|

| VBR  | CR1  |

| EPSR | CR2  |

| FPSR | CR3  |

| EPC  | CR4  |

| FPC  | CR5  |

| SS0  | CR6  |

| SS1  | CR7  |

| SS2  | CR8  |

| SS3  | CR9  |

| SS4  | CR10 |

| GCR  | CR11 |

| GSR  | CR12 |

|      |      |

#### Figure 2-2. Supervisor Additional Resources

M•CORE with M210/M210S Specifications - Rev. 1.0

**Reference Manual**

The following paragraphs describe the supervisor programming model registers. Additional information can be found in **Section 4. Exception Processing**.

#### 2.4.1 Alternate Register File

The alternate register file is provided to reduce the overhead associated with context switching and saving/restoring for time critical tasks. When selected, the alternate register file replaces the general register file for all instructions that normally use a general register. The alternate register file is active when the PSR(AF) bit is set. It is disabled and not accessible when the PSR(AF) bit is cleared. Important parameters and pointer values may be retained in the alternate file and thus are readily accessible when a high-priority task is entered.

In addition, register R0 in the alternate file serves as a stack pointer for the task, making independent stack implementation efficient.