### Freescale Semiconductor Application Note

Document Number: AN3286 Rev. 0.1, 02/2010

# Layout and Design Guidelines for the MC13883

### 1 Introduction

This application note describes guidelines for a Printed Circuit Board (PCB) footprint for the QFN40 package used for the MC13883 integrated charger. Included are layouts of the component copper layer, solder mask, and solder paste stencil. These recommendations are guidelines only and may need to be modified depending on the assembly house used and the other components on the board.

A general description for QFN packages can be found in AN1902 at the Freescale web site:

http://www.freescale.com

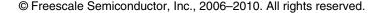

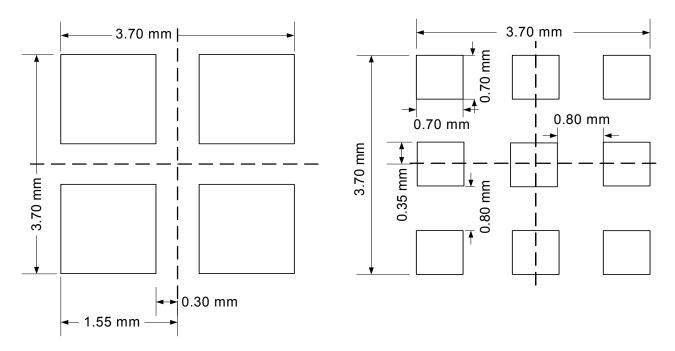

# 2 Component Copper Layer

Figure 1 shows a recommended component copper layer. This layer is also referred to as the top metal layer and is the layer to which the components are soldered. The footprint for the QFN40 package consists of 40 IC contact pads and a centered ground pad.

### **Contents**

| 1 | Introduction                |     | 1 |

|---|-----------------------------|-----|---|

| 2 | Component Copper Layer      |     | 1 |

| 3 | Solder Mask                 | . : | 3 |

| 4 | Solder Paste Stencil        |     | 4 |

| 5 | Problems with Excess Solder | . : | 5 |

| ô | QFN40 Package Dimensions    | . ' | 6 |

| 7 | Layout Considerations       | . ! | 9 |

| 8 | Component Selection         | . ! | 9 |

| a | Document Revision History   | 1   | n |

### **Component Copper Layer**

Figure 1. Component Copper Layer

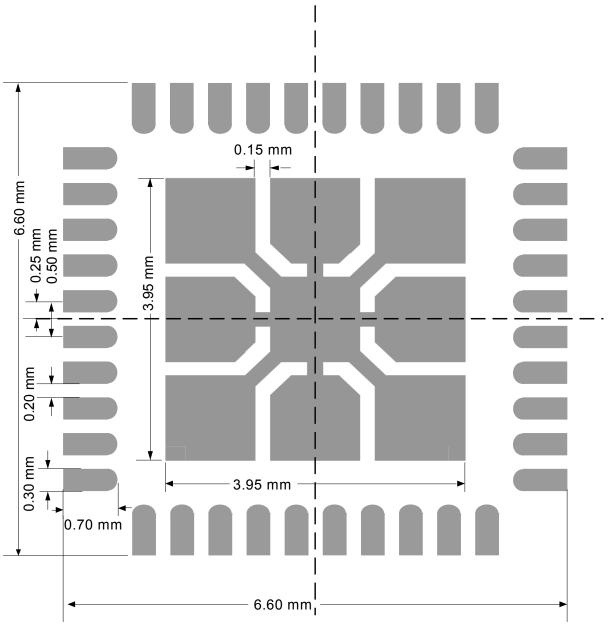

### 3 Solder Mask

The solder mask limits the flow of the solder paste during the reflow process. Figure 2 shows a recommended solder mask pattern. The pattern represents openings in the solder mask. The IC contact openings actually touch, so there is no septum between openings. The lines shown are an artifact of the CAD drawing.

Figure 2. Solder Mask Pattern

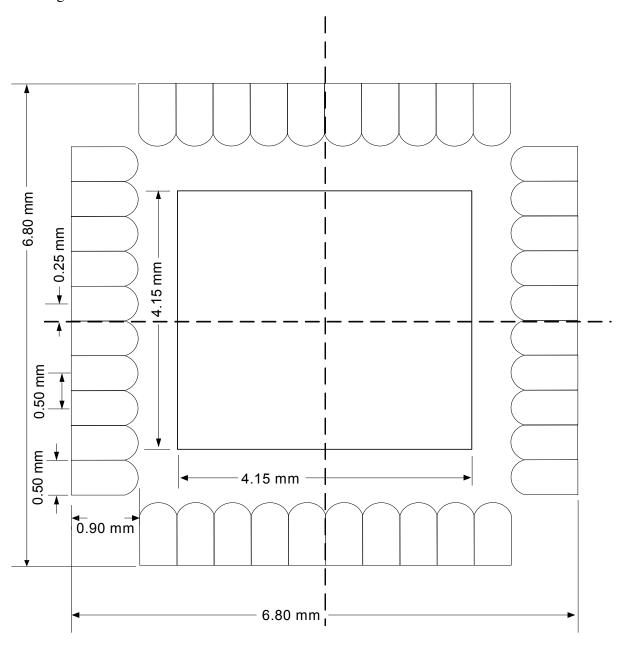

**Solder Paste Stencil**

### 4 Solder Paste Stencil

The solder paste stencil controls the pattern and thickness of the solder paste dispensed on the board. Figure 3 shows a recommended solder stencil pattern. Stencil thickness should be 0.13 mm–0.15 mm. Other patterns and opening sizes can be used if too much solder is being applied. See Section 5, "Problems with Excess Solder," for more information.

Figure 3. Solder Stencil Pattern

### 5 Problems with Excess Solder

Excess solder may cause the QFN to "float" or bridge between the package contacts. To use the correct amount of solder paste applied to the PCB, take into consideration the following:

- Stencil thickness

- Other components mounted on the PCB

- Manufacturing equipment

- Assembly house experience

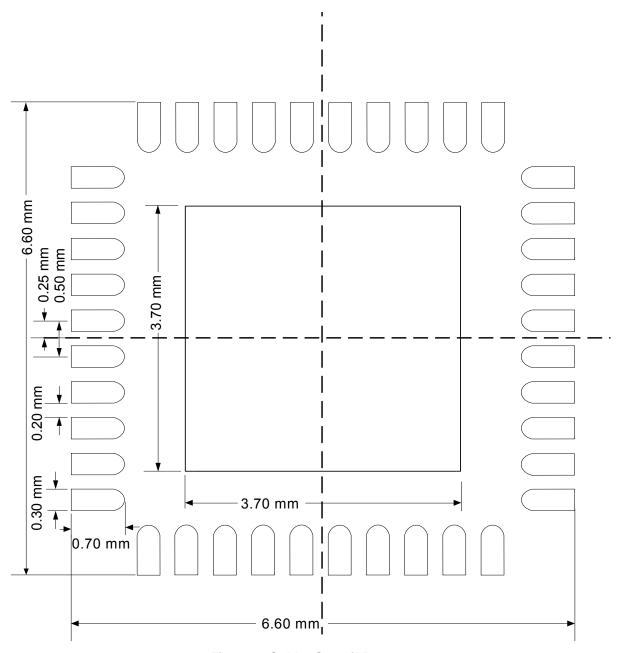

Package floating can be eliminated by reducing the area of solder paste on the centered pad. Figure 4 shows alternative solder stencil patterns to reduce the amount of solder paste applied to the centered pad.

Figure 4. Alternative Solder Stencil Patterns

Solder bridging between package contacts can be reduced by adjusting the metal contact pad widths in Figure 1 from 0.3 mm to 0.25 mm and the solder mask pad openings from 0.5 mm to 0.4 mm. This allows for a 0.1 mm septum of solder mask between the pads. However, this approach may not be feasible for all board houses and may increase assembly cost.

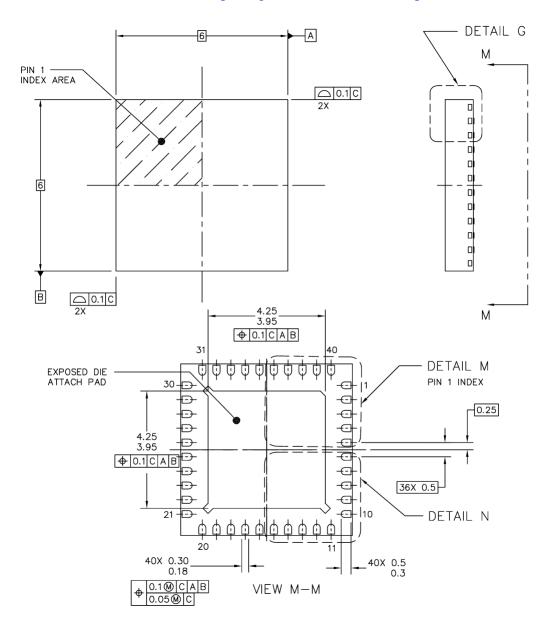

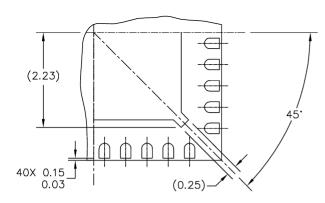

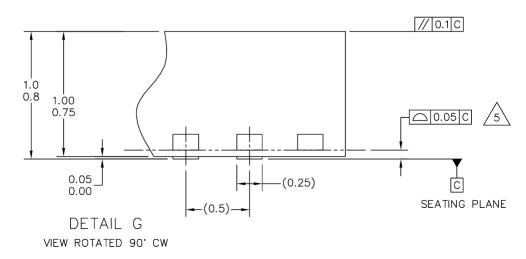

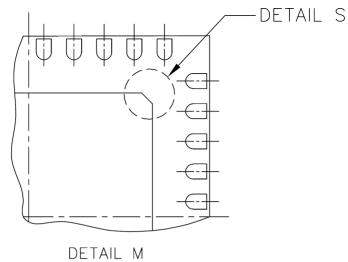

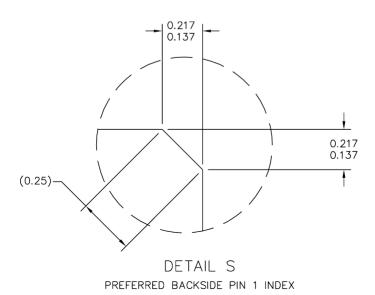

# 6 QFN40 Package Dimensions

Figure 5 through Figure 8 show the QFN40 package dimensions. The package information shown in these figures is available from the Freescale web site at:

http://www.freescale.com/files/shared/doc/package\_info/98ASA10655D.pdf

Figure 5. Outline Dimensions for QFN40, 6x6 mm (Case Outline 1624-01, Issue O)

DETAIL N

PREFERRED CORNER CONFIGURATION

Figure 6. Outline Dimensions for QFN40, 6x6 mm - Continued (Case Outline 1624-01, Issue O)

8

### **QFN40 Package Dimensions**

PREFERRED BACKSIDE PIN 1 INDEX

Figure 7. Outline Dimensions for QFN40, 6x6 mm - Continued (Case Outline 1624-01, Issue O)

Layout and Design Guidelines for the MC13883 Application Note, Rev. 0.1

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THE COMPLETE JEDEC DESIGNATOR FOR THIS PACKAGE IS: HF-PQFN.

CORNER CHAMFER MAY NOT BE PRESENT. DIMENSIONS OF OPTIONAL FEATURES ARE FOR REFERENCE ONLY.

COPLANARITY APPLIES TO LEADS, CORNER LEADS, AND DIE ATTACH PAD.

- 6. FOR ANVIL SINGULATED QFN PACKAGES, MAXIMUM DRAFT ANGLE IS 12'.

- 7. MINIMUM METAL GAP 0.2 MM.

Figure 8. Outline Dimensions for QFN40, 6x6 mm - Continued (Case Outline 1624-01, Issue O)

### 7 Layout Considerations

- DP/DM lines need to be 45 ohms.

- The capacitor on VC should be close to the VC pin.

- The capacitor on BG\_BYP should be close to the BG\_BYP pin.

- The path impedance from VBUS to Battery should be minimized to reduce the voltage drop along this path.

- The impedance in the charge path from ISENSE to BATTP should minimal so that the current is accurately controlled.

- The sense lines from RSENSE to MC13883 should be short and isolated from any noise to maintain the accuracy of the charger. These lines should be connected directly from the pads of RSENSE resistor to the ISENSE and BP pins of the IC.

- No components should be placed on the gates of the control lines CHRGCTRL, BATTFET, BPFET.

## 8 Component Selection

- The 2.2uF capacitor on VBUS must be greater than 1.3uF at 5V.

- The recommend devices for M1, M2, and M4 are as shown in Table 1.

**Table 1. Recommended Devices**

|               | M1      | M2      | М4                |

|---------------|---------|---------|-------------------|

| Combination 1 | Si8415  | Si8401  | Si8401 or FDZ293P |

| Combination 2 | FDZ293P | FDZ293P | Si8401 or FDZ293P |

Layout and Design Guidelines for the MC13883 Application Note, Rev. 0.1

# 9 Document Revision History

Revision 0.1: Copyright date change in preparation for public release.

#### How to Reach Us:

#### **Home Page:**

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The PowerPC name is a trademark of IBM Corp. and is used under license. The described product contains a PowerPC processor core. The PowerPC name is a trademark of IBM Corp. and used under license. The described product is a PowerPC microprocessor. The PowerPC name is a trademark of IBM Corp. and is used under license. The described product is a PowerPC microprocessor core. The PowerPC name is a trademark of IBM Corp. and is used under license.

© Freescale Semiconductor, Inc. 2010. All rights reserved.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see <a href="http://www.freescale.com">http://www.freescale.com</a> or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.